simplify docs/install and merge docs/hardware

docs/hardware is redundant, because it now mostly contains installation instructions, and docs/install also contains hardware information. therefore, in practise, they are both the same kind of information. merge the two, and streamline everything. a lot of redundant information has been removed. docs/install/ has been re-structured in such a way as to enable more chronological reading, to make it easier for the average user to install Canoeboot. This is part of a larger series of changes I'm working on for the documentation. I'm massively auditing the entire Canoeboot documentation. Signed-off-by: Leah Rowe <info@minifree.org>master

parent

c35da8dc01

commit

633dbebbc6

|

|

@ -1,9 +0,0 @@

|

|||

---

|

||||

title: ASUS Chromebook C201

|

||||

x-toc-enable: true

|

||||

...

|

||||

|

||||

This page is absolete. Refer to these pages instead:

|

||||

|

||||

* [C201 flashing instructions](../install/c201.md)

|

||||

* [Chromebook flashing instructions](../install/chromebooks.md)

|

||||

|

|

@ -1,59 +0,0 @@

|

|||

---

|

||||

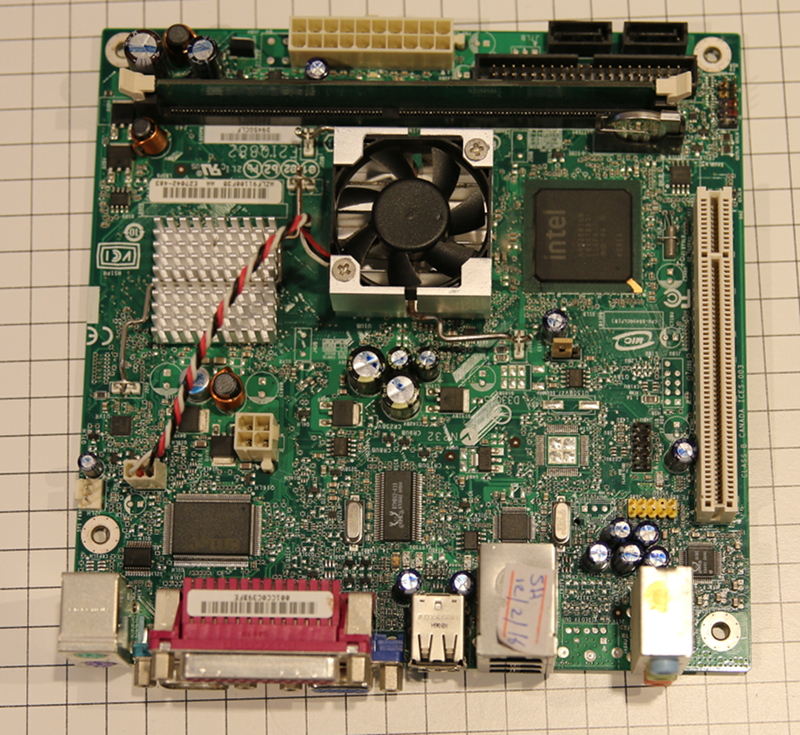

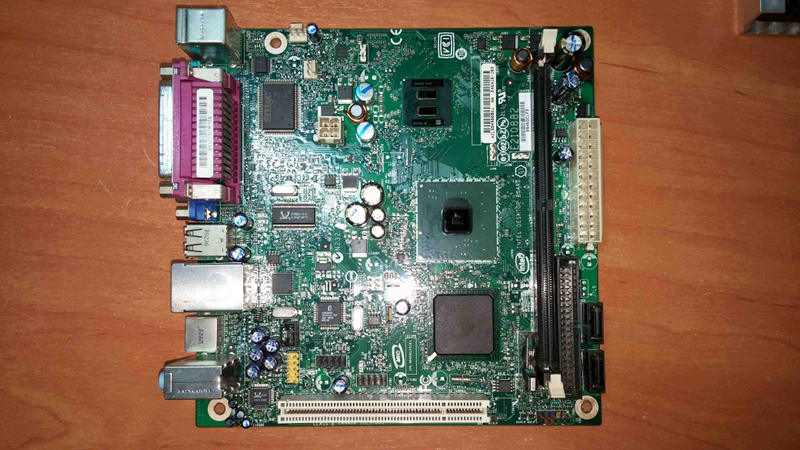

title: Intel D510MO and D410PT desktop boards

|

||||

...

|

||||

|

||||

<div class="specs">

|

||||

<center>

|

||||

![Intel D510MO]()

|

||||

</center>

|

||||

|

||||

| ***Specifications*** | |

|

||||

|----------------------------|------------------------------------------------|

|

||||

| **Manufacturer** | Intel |

|

||||

| **Name** | D510MO/D410PT |

|

||||

| **Released** | 2010 |

|

||||

| **Chipset** | Intel NM10 Express (Mount Olive) |

|

||||

| **CPU** | Intel Atom |

|

||||

| **Graphics** | Integrated |

|

||||

| **Display** | None. |

|

||||

| **Memory** | Up to 4GB |

|

||||

| **Architecture** | x86_64 |

|

||||

| **Original boot firmware** | Intel BIOS |

|

||||

| **Intel ME/AMD PSP** | Not present. |

|

||||

| **Flash chip** | ? |

|

||||

|

||||

```

|

||||

W+: Works;

|

||||

N: Doesn't work;

|

||||

U: Untested;

|

||||

P+: Partially works;

|

||||

```

|

||||

|

||||

| ***Features*** | |

|

||||

|----------------|---------------------------------------|

|

||||

| **Internal flashing with original boot firmware** | N |

|

||||

| **Display** | - |

|

||||

| **Audio** | W+ |

|

||||

| **RAM Init** | P+ |

|

||||

| **External output** | P+ |

|

||||

| **Display brightness** | - |

|

||||

|

||||

| ***Payloads supported*** | |

|

||||

|---------------------------|-------|

|

||||

| **GRUB** | Works |

|

||||

| **SeaBIOS** | Works |

|

||||

| **SeaBIOS with GRUB** | Works |

|

||||

</div>

|

||||

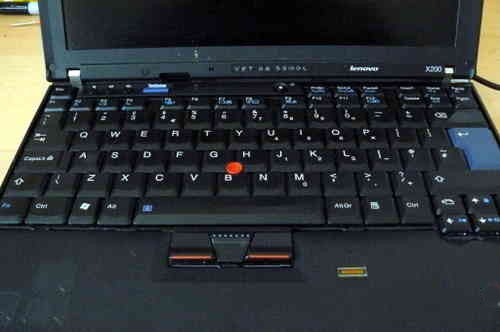

This is a desktop board using intel hardware (circa \~2009, ICH7

|

||||

southbridge, similar performance-wise to the ThinkPad X200. It can make

|

||||

for quite a nifty desktop. Powered by Canoeboot.

|

||||

|

||||

NOTE: D410PT is another name and it's the same board. Flash the exact same

|

||||

ROM and it should work.

|

||||

|

||||

NOTE: This board has a working framebuffer in Grub, but in GNU+Linux in

|

||||

native resolution the display is unusable due to some raminit issues.

|

||||

This board can however be used for building a headless server.

|

||||

|

||||

Flashing instructions can be found at

|

||||

[../install/d510mo.md](../install/d510mo.md)

|

||||

|

|

@ -1,124 +0,0 @@

|

|||

---

|

||||

title: Intel D945GCLF desktop board

|

||||

x-toc-enable: true

|

||||

...

|

||||

|

||||

<div class="specs">

|

||||

<center>

|

||||

<img tabindex=1 alt="D945GCLF" class="p" src="https://av.canoeboot.org/d945gclf/d945gclf.jpg" /><span class="f"><img src="https://av.canoeboot.org/d945gclf/d945gclf.jpg" /></span>

|

||||

</center>

|

||||

|

||||

| ***Specifications*** | |

|

||||

|----------------------------|------------------------------------------------|

|

||||

| **Manufacturer** | Intel |

|

||||

| **Name** | D945GCLF/D945GCLF2D |

|

||||

| **Released** | 2008 |

|

||||

| **Chipset** | Intel Calistoga 945GC |

|

||||

| **CPU** | Intel Atom |

|

||||

| **Graphics** | ? |

|

||||

| **Display** | None. |

|

||||

| **Memory** | Up to 2GB |

|

||||

| **Architecture** | x86_64 |

|

||||

| **Original boot firmware** | Intel BIOS |

|

||||

| **Intel ME/AMD PSP** | Not present. |

|

||||

| **Flash chip** | SOIC-8 512KiB |

|

||||

|

||||

```

|

||||

W+: Works without blobs;

|

||||

N: Doesn't work;

|

||||

W*: Works with blobs;

|

||||

U: Untested;

|

||||

P+: Partially works;

|

||||

P*: Partially works with blobs

|

||||

```

|

||||

|

||||

| ***Features*** | | Notes |

|

||||

|----------------|---------------------------------------|-------|

|

||||

| **Internal flashing with original boot firmware** | N | |

|

||||

| **Display** | - | |

|

||||

| **Audio** | W+ | |

|

||||

| **RAM Init** | W+ | |

|

||||

| **External output** | W+ | |

|

||||

| **Display brightness** | - | |

|

||||

|

||||

| ***Payloads supported*** | |

|

||||

|---------------------------|--------------|

|

||||

| **GRUB** | Doesn't work |

|

||||

| **SeaBIOS** | Works |

|

||||

| **SeaBIOS with GRUB** | Doesn't work |

|

||||

</div>

|

||||

If you just want flashing instructions, go to

|

||||

[../install/d945gclf.md](../install/d945gclf.md)

|

||||

|

||||

D945GCLF2D also reported working by a user.

|

||||

|

||||

Introduction

|

||||

============

|

||||

|

||||

This board is a mini-itx desktop board for 2008. It uses an atom 230,

|

||||

which is a singe core CPU but it is hyperthreaded so it appears to have

|

||||

2 thread to the OS. The flash chip is very small, 512KiB, so grub2 does

|

||||

not fit, which is why Canoeboot has to use seabios on this target. Full

|

||||

disk encryption like on other supported targets will not be possible, so

|

||||

plan accordingly.

|

||||

|

||||

This board has a 945gc chipset which is the desktop equivalent of 945gm

|

||||

which can be found in the Lenovo x60/t60 or macbook2,1. This chipset

|

||||

features an ICH7 southbridge. It has 1 DIMM slot that can accommodate up

|

||||

to 2G of DDR2 RAM.

|

||||

|

||||

Connectivity-wise it has 1 PCI slot, a 10/100 ethernet port, 4 usb slot

|

||||

and 4 usb ports, with one internal header and 2 SATA ports.

|

||||

|

||||

The D945GCLF2 is an upgraded version of this board. The differences are:

|

||||

1 more USB header, 10/100/1000 ethernet and a dual core cpu (also

|

||||

hyperthreaded). Since the board is almost identical (and coreboot code

|

||||

seem to indicate that it works, since MAX\_CPU=4 is set), it is believed

|

||||

that it should also work but this is untested.

|

||||

|

||||

Remarks about vendor bios:

|

||||

--------------------------

|

||||

|

||||

- Without a coreboot firmware this board is completely useless, since the

|

||||

vendor bios is very bad. It cannot boot from any HDD whether it is

|

||||

connected to the SATA port or USB. With Canoeboot, it works just

|

||||

fine.

|

||||

|

||||

- The vendor bios write protects the flash so it requires external

|

||||

flashing to install Canoeboot on this device. Once Canoeboot is

|

||||

flashed there is no problem to update the firmware internally

|

||||

|

||||

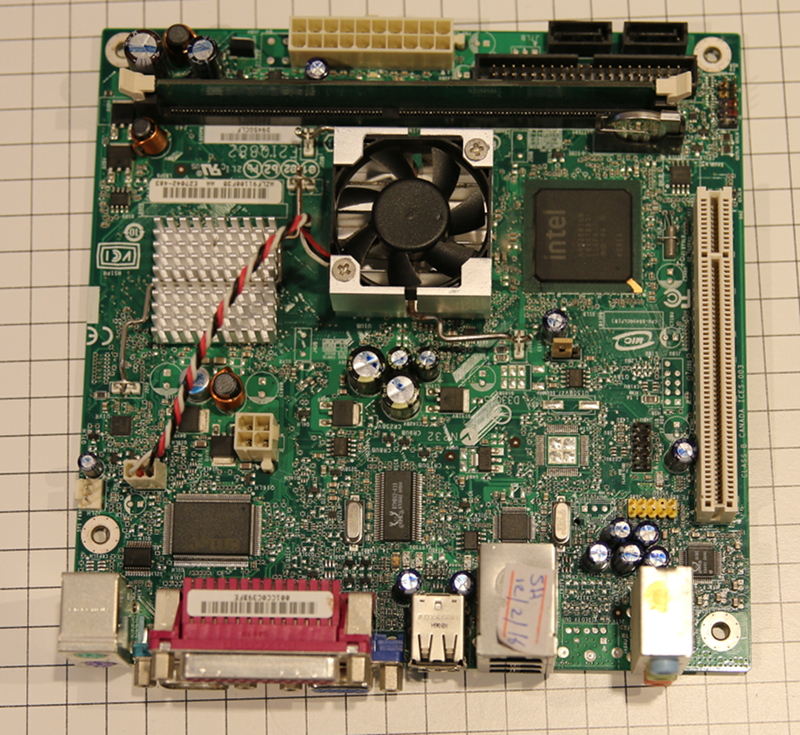

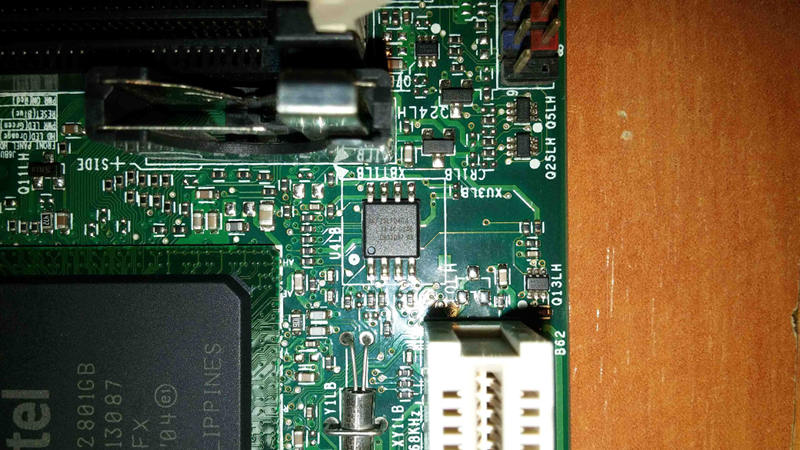

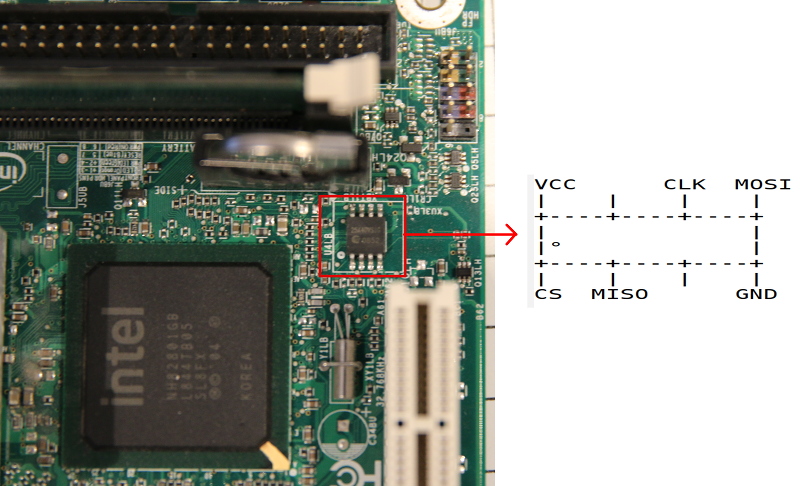

Here is an image of the board:\

|

||||

\

|

||||

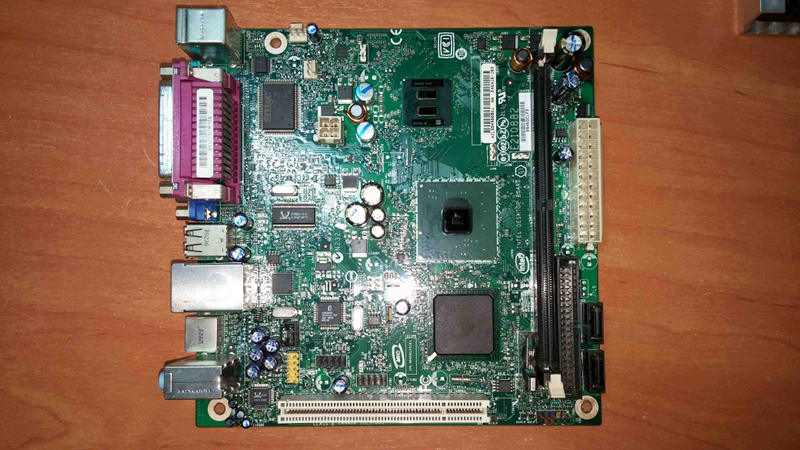

Here is an image of the D945GCLF2 board:\

|

||||

{width="80%" height="80%"}\

|

||||

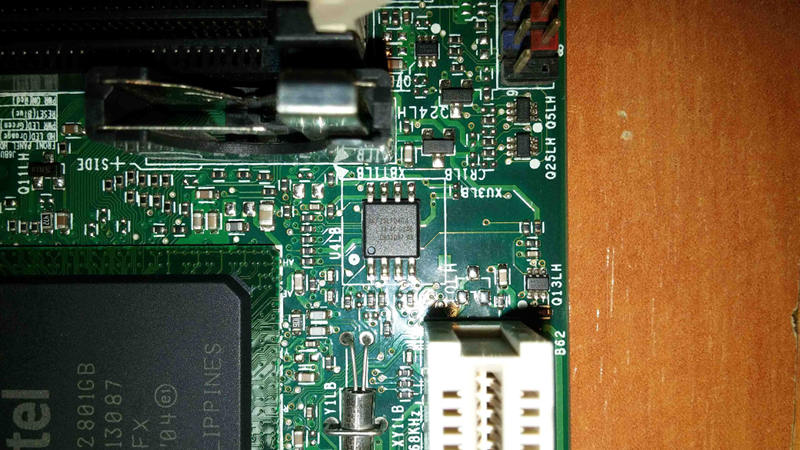

And SPI SOIC8 flash chip\

|

||||

{width="50%" height="50%"}

|

||||

|

||||

How to replace thermal paste and fan

|

||||

------------------------------------

|

||||

|

||||

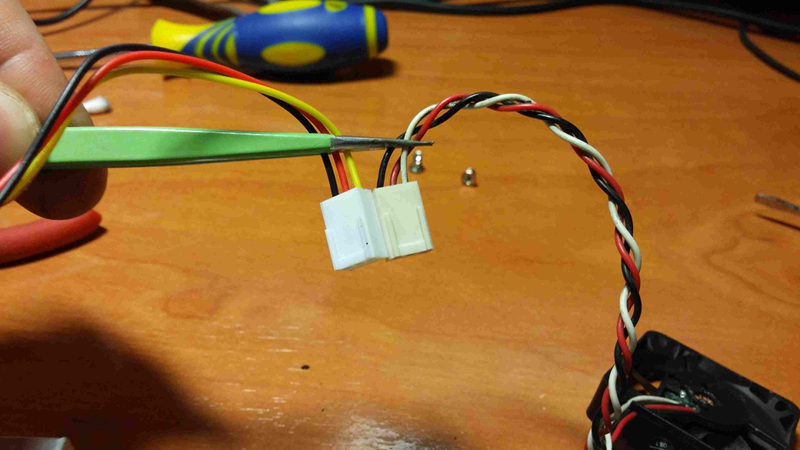

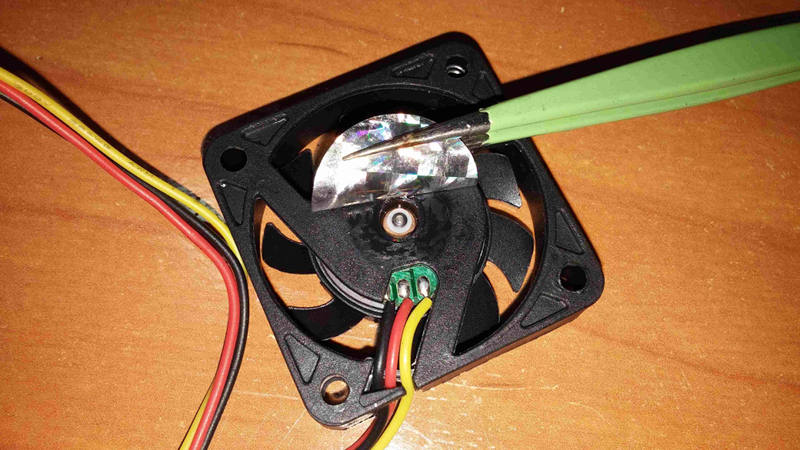

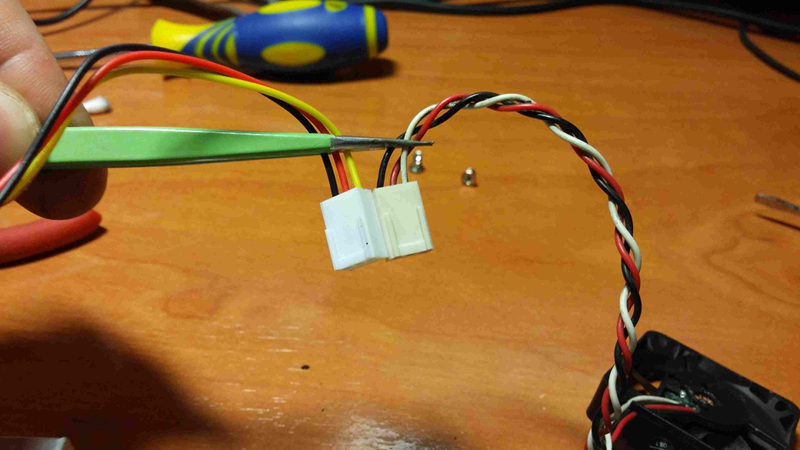

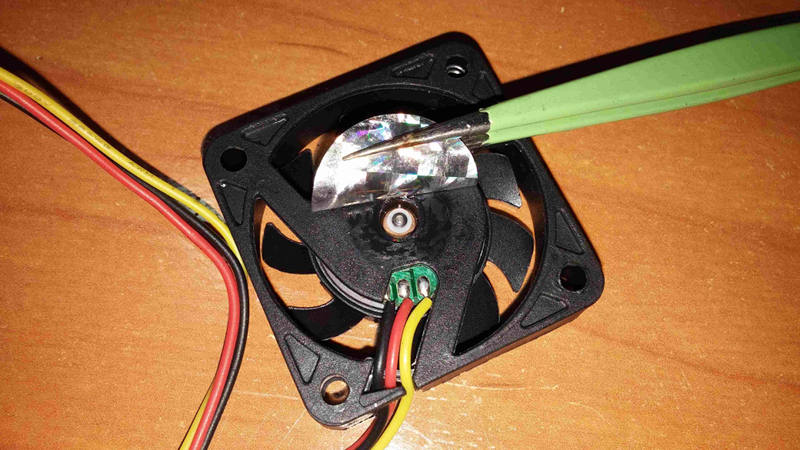

This board comes with very crappy disposable loud fan, that one has no

|

||||

bearings, which can not be repaired or oiled properly, do not waste your

|

||||

time trying to fix it, just buy one chinese same size fan\

|

||||

{width="50%" height="50%"}

|

||||

{width="50%" height="50%"}\

|

||||

Make sure that new one has same wiring\

|

||||

{width="50%" height="50%"}\

|

||||

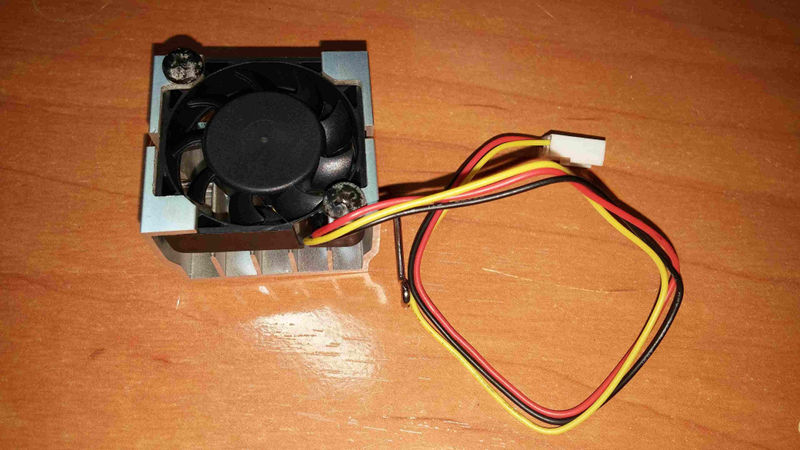

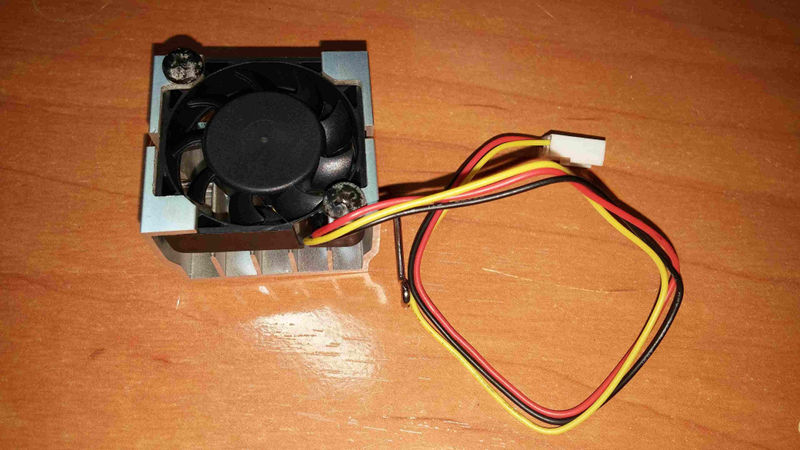

This is a new one, with bearing and maintenable\

|

||||

{width="50%" height="50%"}

|

||||

{width="50%" height="50%"}\

|

||||

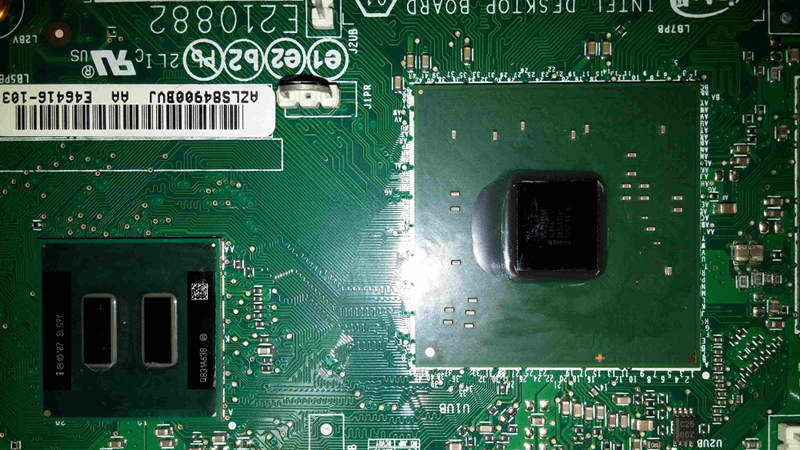

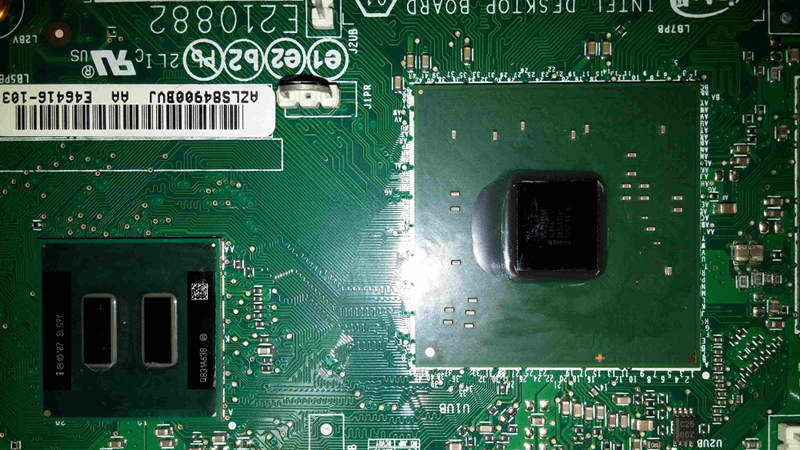

Now remove the both coolers rotating them a bit, slowly, then clean both

|

||||

silicons and both coolers (removing cmos battery first is recommended)\

|

||||

{width="50%" height="50%"}\

|

||||

Put a little bit of non conductive thermal paste on both silicons (only

|

||||

cpu silicon iis shown on that image)\

|

||||

{width="50%" height="50%"}\

|

||||

|

||||

Before assembling new fan, some need new longer screws, make sure having

|

||||

these (on the left is original one, too short for new fan)\

|

||||

{width="50%" height="50%"}\

|

||||

After that, assemble your new fan into CPU cooler\

|

||||

{width="50%" height="50%"}\

|

||||

Finally assemle both coolers on both chips, do not forget put in the CPU

|

||||

fan connector back, and you are done.

|

||||

|

|

@ -1,102 +0,0 @@

|

|||

---

|

||||

title: Gigabyte GA-G41M-ES2L desktop board

|

||||

...

|

||||

|

||||

<div class="specs">

|

||||

<center>

|

||||

![GA-G41M-ES2L]()

|

||||

</center>

|

||||

|

||||

| ***Specifications*** | |

|

||||

|----------------------------|------------------------------------------------|

|

||||

| **Manufacturer** | Gigabyte |

|

||||

| **Name** | GA-G41M-ES2L |

|

||||

| **Released** | 2009 |

|

||||

| **Chipset** | Intel G41 |

|

||||

| **CPU** | Intel Core 2 Extreme/Quad/Duo,

|

||||

Pentium Extreme/D/4 Extreme/4/Celeron |

|

||||

| **Graphics** | Integrated |

|

||||

| **Display** | None. |

|

||||

| **Memory** | Up to 8GB (2x4GB DDR2-800) |

|

||||

| **Architecture** | x86_64 |

|

||||

| **Original boot firmware** | AWARD BIOS |

|

||||

| **Intel ME/AMD PSP** | Present. Can be disabled |

|

||||

| **Flash chip** | 2x8Mbit |

|

||||

|

||||

```

|

||||

W+: Works;

|

||||

N: Doesn't work;

|

||||

U: Untested;

|

||||

P+: Partially works;

|

||||

```

|

||||

|

||||

| ***Features*** | |

|

||||

|----------------|---------------------------------------|

|

||||

| **Internal flashing with original boot firmware** | W+ |

|

||||

| **Display** | - |

|

||||

| **Audio** | W+ |

|

||||

| **RAM Init** | P+ |

|

||||

| **External output** | P+ |

|

||||

| **Display brightness** | - |

|

||||

|

||||

| ***Payloads supported*** | |

|

||||

|---------------------------|-------|

|

||||

| **GRUB** | Slow! |

|

||||

| **SeaBIOS** | Works |

|

||||

| **SeaBIOS with GRUB** | Works |

|

||||

</div>

|

||||

This is a desktop board using intel hardware (circa \~2009, ICH7

|

||||

southbridge, similar performance-wise to the ThinkPad X200. It can make

|

||||

for quite a nifty desktop. Powered by Canoeboot.

|

||||

|

||||

In recent Canoeboot releases, only SeaBIOS payload is provided in ROMs

|

||||

for this board. According to user reports, they work quite well. GRUB was

|

||||

always buggy on this board, so it was removed from cbmk.

|

||||

|

||||

IDE on the board is untested, but it might be possible to use a SATA HDD

|

||||

using an IDE SATA adapter. The SATA ports do work, but it's IDE emulation. The

|

||||

emulation is slow in DMA mode sia SeaBIOS, so SeaBIOS is configured to use PIO

|

||||

mode on this board. This SeaBIOS configuration does not affect the GNU+Linux kernel.

|

||||

|

||||

You need to set a custom MAC address in GNU+Linux for the NIC to work.

|

||||

In /etc/network/interfaces on debian-based systems like Debian or

|

||||

Devuan, this would be in the entry for your NIC:\

|

||||

hwaddress ether macaddressgoeshere

|

||||

|

||||

Alternatively:

|

||||

|

||||

cbfstool canoeboot.rom extract -n rt8168-macaddress -f rt8168-macaddress

|

||||

|

||||

Modify the MAC address in the file `rt8168-macaddress` and then:

|

||||

|

||||

cbfstool canoeboot.rom remove -n rt8168-macaddress

|

||||

cbfstool canoeboot.rom add -f rt8168-macaddress -n rt8168-macaddress -t raw

|

||||

|

||||

Now you have a different MAC address hardcoded. In the above example, the ROM

|

||||

image is named `canoeboot.rom` for your board. You can find cbfstool

|

||||

under `coreboot/default/util/cbfstool/` after running the following command

|

||||

in the build system:

|

||||

|

||||

./update trees -d coreboot TREENAME

|

||||

|

||||

You can learn more about using the build system, cbmk, here:\

|

||||

[Canoeboot build instructions](../build/)

|

||||

|

||||

Flashing instructions can be found at

|

||||

[../install/](../install/)

|

||||

|

||||

RAM

|

||||

---

|

||||

|

||||

**This board is very picky with RAM. If it doesn't boot, try an EHCI debug

|

||||

dongle, serial usb adapter and null modem cable, or spkmodem, to get a

|

||||

coreboot log to see if it passed raminit.**

|

||||

|

||||

Kingston 8 GiB Kit KVR800D2N6/8G with Elpida Chips E2108ABSE-8G-E

|

||||

|

||||

this is a 2x4GB setup and these work quite well, according to a user on IRC.

|

||||

|

||||

Nanya NT2GT64U8HD0BY-AD with 2 GiB of NT5TU128M8DE-AD chips works too.

|

||||

|

||||

Many other modules will probably work just fine, but raminit is very picky on

|

||||

this board. Your mileage *will* fluctuate, wildly.

|

||||

|

|

@ -1,24 +0,0 @@

|

|||

# biosdecode 2.12

|

||||

VPD present.

|

||||

BIOS Build ID: 6DET65WW

|

||||

Box Serial Number: L3AAR0B

|

||||

Motherboard Serial Number: 1ZFDS89N4DD

|

||||

Machine Type/Model: 7459GW4

|

||||

SMBIOS 2.4 present.

|

||||

Structure Table Length: 2464 bytes

|

||||

Structure Table Address: 0x000E0010

|

||||

Number Of Structures: 68

|

||||

Maximum Structure Size: 120 bytes

|

||||

BIOS32 Service Directory present.

|

||||

Revision: 0

|

||||

Calling Interface Address: 0x000FDC80

|

||||

ACPI 2.0 present.

|

||||

OEM Identifier: LENOVO

|

||||

RSD Table 32-bit Address: 0x79B5B843

|

||||

XSD Table 64-bit Address: 0x0000000079B5B8AB

|

||||

PNP BIOS 1.0 present.

|

||||

Event Notification: Not Supported

|

||||

Real Mode 16-bit Code Address: E2CA:1868

|

||||

Real Mode 16-bit Data Address: 0040:0000

|

||||

16-bit Protected Mode Code Address: 0x000F97BD

|

||||

16-bit Protected Mode Data Address: 0x00000400

|

||||

|

|

@ -1,208 +0,0 @@

|

|||

Codec: Conexant CX20561 (Hermosa)

|

||||

Address: 0

|

||||

AFG Function Id: 0x1 (unsol 1)

|

||||

MFG Function Id: 0x2 (unsol 1)

|

||||

Vendor Id: 0x14f15051

|

||||

Subsystem Id: 0x17aa20ff

|

||||

Revision Id: 0x100000

|

||||

Modem Function Group: 0x2

|

||||

Default PCM:

|

||||

rates [0x160]: 44100 48000 96000

|

||||

bits [0xe]: 16 20 24

|

||||

formats [0x1]: PCM

|

||||

Default Amp-In caps: N/A

|

||||

Default Amp-Out caps: N/A

|

||||

State of AFG node 0x01:

|

||||

Power states: D0 D1 D2 D3 CLKSTOP

|

||||

Power: setting=D0, actual=D0

|

||||

GPIO: io=4, o=0, i=0, unsolicited=1, wake=0

|

||||

IO[0]: enable=0, dir=0, wake=0, sticky=0, data=0, unsol=0

|

||||

IO[1]: enable=0, dir=0, wake=0, sticky=0, data=0, unsol=0

|

||||

IO[2]: enable=0, dir=0, wake=0, sticky=0, data=0, unsol=0

|

||||

IO[3]: enable=0, dir=0, wake=0, sticky=0, data=0, unsol=0

|

||||

Node 0x10 [Audio Output] wcaps 0xc1d: Stereo Amp-Out R/L

|

||||

Control: name="Speaker Playback Volume", index=0, device=0

|

||||

ControlAmp: chs=3, dir=Out, idx=0, ofs=0

|

||||

Control: name="Speaker Playback Switch", index=0, device=0

|

||||

ControlAmp: chs=3, dir=Out, idx=0, ofs=0

|

||||

Device: name="CX20561 Analog", type="Audio", device=0

|

||||

Amp-Out caps: ofs=0x4a, nsteps=0x4a, stepsize=0x03, mute=0

|

||||

Amp-Out vals: [0x4a 0x4a]

|

||||

Converter: stream=8, channel=0

|

||||

PCM:

|

||||

rates [0x560]: 44100 48000 96000 192000

|

||||

bits [0xe]: 16 20 24

|

||||

formats [0x1]: PCM

|

||||

Power states: D0 D1 D2 D3

|

||||

Power: setting=D0, actual=D0

|

||||

Node 0x11 [Audio Output] wcaps 0xc1d: Stereo Amp-Out R/L

|

||||

Control: name="Headphone Playback Volume", index=0, device=0

|

||||

ControlAmp: chs=3, dir=Out, idx=0, ofs=0

|

||||

Control: name="Headphone Playback Switch", index=0, device=0

|

||||

ControlAmp: chs=3, dir=Out, idx=0, ofs=0

|

||||

Amp-Out caps: ofs=0x4a, nsteps=0x4a, stepsize=0x03, mute=0

|

||||

Amp-Out vals: [0x4a 0x4a]

|

||||

Converter: stream=8, channel=0

|

||||

PCM:

|

||||

rates [0x560]: 44100 48000 96000 192000

|

||||

bits [0xe]: 16 20 24

|

||||

formats [0x1]: PCM

|

||||

Power states: D0 D1 D2 D3

|

||||

Power: setting=D0, actual=D0

|

||||

Node 0x12 [Audio Output] wcaps 0x211: Stereo Digital

|

||||

Control: name="IEC958 Playback Con Mask", index=0, device=0

|

||||

Control: name="IEC958 Playback Pro Mask", index=0, device=0

|

||||

Control: name="IEC958 Playback Default", index=0, device=0

|

||||

Control: name="IEC958 Playback Switch", index=0, device=0

|

||||

Control: name="IEC958 Default PCM Playback Switch", index=0, device=0

|

||||

Device: name="CX20561 Digital", type="SPDIF", device=1

|

||||

Converter: stream=8, channel=0

|

||||

Digital:

|

||||

Digital category: 0x0

|

||||

IEC Coding Type: 0x0

|

||||

PCM:

|

||||

rates [0x160]: 44100 48000 96000

|

||||

bits [0xe]: 16 20 24

|

||||

formats [0x5]: PCM AC3

|

||||

Node 0x13 [Beep Generator Widget] wcaps 0x70000c: Mono Amp-Out

|

||||

Control: name="Beep Playback Volume", index=0, device=0

|

||||

ControlAmp: chs=1, dir=Out, idx=0, ofs=0

|

||||

Control: name="Beep Playback Switch", index=0, device=0

|

||||

ControlAmp: chs=1, dir=Out, idx=0, ofs=0

|

||||

Amp-Out caps: ofs=0x03, nsteps=0x03, stepsize=0x17, mute=0

|

||||

Amp-Out vals: [0x00]

|

||||

Node 0x14 [Audio Input] wcaps 0x100d1b: Stereo Amp-In R/L

|

||||

Device: name="CX20561 Analog", type="Audio", device=0

|

||||

Amp-In caps: ofs=0x4a, nsteps=0x50, stepsize=0x03, mute=0

|

||||

Amp-In vals: [0x50 0x50] [0x50 0x50]

|

||||

Converter: stream=4, channel=0

|

||||

SDI-Select: 0

|

||||

PCM:

|

||||

rates [0x160]: 44100 48000 96000

|

||||

bits [0xe]: 16 20 24

|

||||

formats [0x1]: PCM

|

||||

Power states: D0 D1 D2 D3

|

||||

Power: setting=D0, actual=D0

|

||||

Connection: 2

|

||||

0x1d* 0x17

|

||||

Node 0x15 [Audio Input] wcaps 0x100d1b: Stereo Amp-In R/L

|

||||

Control: name="Capture Volume", index=0, device=0

|

||||

ControlAmp: chs=3, dir=In, idx=1, ofs=0

|

||||

Amp-In caps: ofs=0x4a, nsteps=0x50, stepsize=0x03, mute=0

|

||||

Amp-In vals: [0x50 0x50]

|

||||

Converter: stream=0, channel=0

|

||||

SDI-Select: 0

|

||||

PCM:

|

||||

rates [0x160]: 44100 48000 96000

|

||||

bits [0xe]: 16 20 24

|

||||

formats [0x1]: PCM

|

||||

Power states: D0 D1 D2 D3

|

||||

Power: setting=D0, actual=D0

|

||||

Connection: 1

|

||||

0x18

|

||||

Node 0x16 [Pin Complex] wcaps 0x400581: Stereo

|

||||

Control: name="Headphone Jack", index=0, device=0

|

||||

Pincap 0x0000001c: OUT HP Detect

|

||||

Pin Default 0x042140f0: [Jack] HP Out at Ext Right

|

||||

Conn = 1/8, Color = Green

|

||||

DefAssociation = 0xf, Sequence = 0x0

|

||||

Pin-ctls: 0xc0: OUT HP

|

||||

Unsolicited: tag=02, enabled=1

|

||||

Power states: D0 D1 D2 D3

|

||||

Power: setting=D0, actual=D0

|

||||

Connection: 2

|

||||

0x10 0x11*

|

||||

Node 0x17 [Pin Complex] wcaps 0x40048b: Stereo Amp-In

|

||||

Control: name="Dock Mic Boost Volume", index=0, device=0

|

||||

ControlAmp: chs=3, dir=In, idx=0, ofs=0

|

||||

Control: name="Dock Mic Jack", index=0, device=0

|

||||

Amp-In caps: ofs=0x00, nsteps=0x04, stepsize=0x27, mute=0

|

||||

Amp-In vals: [0x00 0x00]

|

||||

Pincap 0x00001224: IN Detect

|

||||

Vref caps: 50 80

|

||||

Pin Default 0x61a190f0: [N/A] Mic at Sep Rear

|

||||

Conn = 1/8, Color = Pink

|

||||

DefAssociation = 0xf, Sequence = 0x0

|

||||

Pin-ctls: 0x24: IN VREF_80

|

||||

Unsolicited: tag=03, enabled=1

|

||||

Power states: D0 D1 D2 D3

|

||||

Power: setting=D0, actual=D0

|

||||

Node 0x18 [Pin Complex] wcaps 0x40048b: Stereo Amp-In

|

||||

Control: name="Mic Boost Volume", index=0, device=0

|

||||

ControlAmp: chs=3, dir=In, idx=0, ofs=0

|

||||

Control: name="Mic Jack", index=0, device=0

|

||||

Amp-In caps: ofs=0x00, nsteps=0x04, stepsize=0x27, mute=0

|

||||

Amp-In vals: [0x00 0x00]

|

||||

Pincap 0x00001224: IN Detect

|

||||

Vref caps: 50 80

|

||||

Pin Default 0x04a190f0: [Jack] Mic at Ext Right

|

||||

Conn = 1/8, Color = Pink

|

||||

DefAssociation = 0xf, Sequence = 0x0

|

||||

Pin-ctls: 0x24: IN VREF_80

|

||||

Unsolicited: tag=04, enabled=1

|

||||

Power states: D0 D1 D2 D3

|

||||

Power: setting=D0, actual=D0

|

||||

Node 0x19 [Pin Complex] wcaps 0x400581: Stereo

|

||||

Control: name="Dock Headphone Jack", index=0, device=0

|

||||

Pincap 0x00000014: OUT Detect

|

||||

Pin Default 0x612140f0: [N/A] HP Out at Sep Rear

|

||||

Conn = 1/8, Color = Green

|

||||

DefAssociation = 0xf, Sequence = 0x0

|

||||

Pin-ctls: 0x40: OUT

|

||||

Unsolicited: tag=01, enabled=1

|

||||

Power states: D0 D1 D2 D3

|

||||

Power: setting=D0, actual=D0

|

||||

Connection: 2

|

||||

0x10 0x11*

|

||||

Node 0x1a [Pin Complex] wcaps 0x400501: Stereo

|

||||

Control: name="Speaker Phantom Jack", index=0, device=0

|

||||

Pincap 0x00010010: OUT EAPD

|

||||

EAPD 0x2: EAPD

|

||||

Pin Default 0x901701f0: [Fixed] Speaker at Int N/A

|

||||

Conn = Analog, Color = Unknown

|

||||

DefAssociation = 0xf, Sequence = 0x0

|

||||

Misc = NO_PRESENCE

|

||||

Pin-ctls: 0x40: OUT

|

||||

Power states: D0 D1 D2 D3

|

||||

Power: setting=D0, actual=D0

|

||||

Connection: 2

|

||||

0x10* 0x11

|

||||

Node 0x1b [Pin Complex] wcaps 0x400500: Mono

|

||||

Pincap 0x00010010: OUT EAPD

|

||||

EAPD 0x2: EAPD

|

||||

Pin Default 0x40f001f0: [N/A] Other at Ext N/A

|

||||

Conn = Unknown, Color = Unknown

|

||||

DefAssociation = 0xf, Sequence = 0x0

|

||||

Misc = NO_PRESENCE

|

||||

Pin-ctls: 0x40: OUT

|

||||

Power states: D0 D1 D2 D3

|

||||

Power: setting=D0, actual=D0

|

||||

Connection: 2

|

||||

0x10* 0x11

|

||||

Node 0x1c [Pin Complex] wcaps 0x400701: Stereo Digital

|

||||

Control: name="SPDIF Phantom Jack", index=0, device=0

|

||||

Pincap 0x00000010: OUT

|

||||

Pin Default 0x40f001f0: [N/A] Other at Ext N/A

|

||||

Conn = Unknown, Color = Unknown

|

||||

DefAssociation = 0xf, Sequence = 0x0

|

||||

Misc = NO_PRESENCE

|

||||

Pin-ctls: 0x40: OUT

|

||||

Power states: D0 D1 D2 D3

|

||||

Power: setting=D0, actual=D0

|

||||

Connection: 1

|

||||

0x12

|

||||

Node 0x1d [Pin Complex] wcaps 0x40040b: Stereo Amp-In

|

||||

Control: name="Internal Mic Boost Volume", index=0, device=0

|

||||

ControlAmp: chs=3, dir=In, idx=0, ofs=0

|

||||

Control: name="Internal Mic Phantom Jack", index=0, device=0

|

||||

Amp-In caps: ofs=0x00, nsteps=0x04, stepsize=0x2f, mute=0

|

||||

Amp-In vals: [0x00 0x00]

|

||||

Pincap 0x00000020: IN

|

||||

Pin Default 0x90a601f0: [Fixed] Mic at Int N/A

|

||||

Conn = Digital, Color = Unknown

|

||||

DefAssociation = 0xf, Sequence = 0x0

|

||||

Misc = NO_PRESENCE

|

||||

Pin-ctls: 0x20: IN

|

||||

Power states: D0 D1 D2 D3

|

||||

Power: setting=D0, actual=D0

|

||||

Node 0x1e [Vendor Defined Widget] wcaps 0xf00000: Mono

|

||||

|

|

@ -1,52 +0,0 @@

|

|||

processor : 0

|

||||

vendor_id : GenuineIntel

|

||||

cpu family : 6

|

||||

model : 23

|

||||

model name : Intel(R) Core(TM)2 Duo CPU P8600 @ 2.40GHz

|

||||

stepping : 6

|

||||

microcode : 0x60c

|

||||

cpu MHz : 800.000

|

||||

cache size : 3072 KB

|

||||

physical id : 0

|

||||

siblings : 2

|

||||

core id : 0

|

||||

cpu cores : 2

|

||||

apicid : 0

|

||||

initial apicid : 0

|

||||

fpu : yes

|

||||

fpu_exception : yes

|

||||

cpuid level : 10

|

||||

wp : yes

|

||||

flags : fpu vme de pse tsc msr pae mce cx8 apic sep mtrr pge mca cmov pat pse36 clflush dts acpi mmx fxsr sse sse2 ss ht tm pbe syscall nx lm constant_tsc arch_perfmon pebs bts nopl aperfmperf pni dtes64 monitor ds_cpl vmx smx est tm2 ssse3 cx16 xtpr pdcm sse4_1 lahf_lm dtherm tpr_shadow vnmi flexpriority

|

||||

bogomips : 4787.97

|

||||

clflush size : 64

|

||||

cache_alignment : 64

|

||||

address sizes : 36 bits physical, 48 bits virtual

|

||||

power management:

|

||||

|

||||

processor : 1

|

||||

vendor_id : GenuineIntel

|

||||

cpu family : 6

|

||||

model : 23

|

||||

model name : Intel(R) Core(TM)2 Duo CPU P8600 @ 2.40GHz

|

||||

stepping : 6

|

||||

microcode : 0x60c

|

||||

cpu MHz : 1600.000

|

||||

cache size : 3072 KB

|

||||

physical id : 0

|

||||

siblings : 2

|

||||

core id : 1

|

||||

cpu cores : 2

|

||||

apicid : 1

|

||||

initial apicid : 1

|

||||

fpu : yes

|

||||

fpu_exception : yes

|

||||

cpuid level : 10

|

||||

wp : yes

|

||||

flags : fpu vme de pse tsc msr pae mce cx8 apic sep mtrr pge mca cmov pat pse36 clflush dts acpi mmx fxsr sse sse2 ss ht tm pbe syscall nx lm constant_tsc arch_perfmon pebs bts nopl aperfmperf pni dtes64 monitor ds_cpl vmx smx est tm2 ssse3 cx16 xtpr pdcm sse4_1 lahf_lm dtherm tpr_shadow vnmi flexpriority

|

||||

bogomips : 4787.97

|

||||

clflush size : 64

|

||||

cache_alignment : 64

|

||||

address sizes : 36 bits physical, 48 bits virtual

|

||||

power management:

|

||||

|

||||

File diff suppressed because it is too large

Load Diff

|

|

@ -1,587 +0,0 @@

|

|||

# dmidecode 2.12

|

||||

SMBIOS 2.4 present.

|

||||

68 structures occupying 2464 bytes.

|

||||

Table at 0x000E0010.

|

||||

|

||||

Handle 0x0000, DMI type 0, 24 bytes

|

||||

BIOS Information

|

||||

Vendor: LENOVO

|

||||

Version: 6DET65WW (3.15 )

|

||||

Release Date: 08/24/2010

|

||||

Address: 0xE0000

|

||||

Runtime Size: 128 kB

|

||||

ROM Size: 8192 kB

|

||||

Characteristics:

|

||||

PCI is supported

|

||||

PC Card (PCMCIA) is supported

|

||||

PNP is supported

|

||||

BIOS is upgradeable

|

||||

BIOS shadowing is allowed

|

||||

ESCD support is available

|

||||

Boot from CD is supported

|

||||

Selectable boot is supported

|

||||

BIOS ROM is socketed

|

||||

EDD is supported

|

||||

ACPI is supported

|

||||

USB legacy is supported

|

||||

BIOS boot specification is supported

|

||||

Targeted content distribution is supported

|

||||

BIOS Revision: 3.21

|

||||

Firmware Revision: 1.6

|

||||

|

||||

Handle 0x0001, DMI type 1, 27 bytes

|

||||

System Information

|

||||

Manufacturer: LENOVO

|

||||

Product Name: 7459GW4

|

||||

Version: ThinkPad X200

|

||||

Serial Number: L3AAR0B

|

||||

UUID: 93861E01-4A15-11CB-8F2C-D4BC407E0839

|

||||

Wake-up Type: Power Switch

|

||||

SKU Number: Not Specified

|

||||

Family: ThinkPad X200

|

||||

|

||||

Handle 0x0002, DMI type 2, 8 bytes

|

||||

Base Board Information

|

||||

Manufacturer: LENOVO

|

||||

Product Name: 7459GW4

|

||||

Version: Not Available

|

||||

Serial Number: 1ZFDS89N4DD

|

||||

|

||||

Handle 0x0003, DMI type 3, 13 bytes

|

||||

Chassis Information

|

||||

Manufacturer: LENOVO

|

||||

Type: Notebook

|

||||

Lock: Not Present

|

||||

Version: Not Available

|

||||

Serial Number: Not Available

|

||||

Asset Tag: 1S7459GW4L3AAR0B

|

||||

Boot-up State: Unknown

|

||||

Power Supply State: Unknown

|

||||

Thermal State: Unknown

|

||||

Security Status: Unknown

|

||||

|

||||

Handle 0x0004, DMI type 126, 13 bytes

|

||||

Inactive

|

||||

|

||||

Handle 0x0005, DMI type 126, 13 bytes

|

||||

Inactive

|

||||

|

||||

Handle 0x0006, DMI type 4, 35 bytes

|

||||

Processor Information

|

||||

Socket Designation: None

|

||||

Type: Central Processor

|

||||

Family: Other

|

||||

Manufacturer: GenuineIntel

|

||||

ID: 76 06 01 00 FF FB EB BF

|

||||

Signature: Type 0, Family 6, Model 23, Stepping 6

|

||||

Flags:

|

||||

FPU (Floating-point unit on-chip)

|

||||

VME (Virtual mode extension)

|

||||

DE (Debugging extension)

|

||||

PSE (Page size extension)

|

||||

TSC (Time stamp counter)

|

||||

MSR (Model specific registers)

|

||||

PAE (Physical address extension)

|

||||

MCE (Machine check exception)

|

||||

CX8 (CMPXCHG8 instruction supported)

|

||||

APIC (On-chip APIC hardware supported)

|

||||

SEP (Fast system call)

|

||||

MTRR (Memory type range registers)

|

||||

PGE (Page global enable)

|

||||

MCA (Machine check architecture)

|

||||

CMOV (Conditional move instruction supported)

|

||||

PAT (Page attribute table)

|

||||

PSE-36 (36-bit page size extension)

|

||||

CLFSH (CLFLUSH instruction supported)

|

||||

DS (Debug store)

|

||||

ACPI (ACPI supported)

|

||||

MMX (MMX technology supported)

|

||||

FXSR (FXSAVE and FXSTOR instructions supported)

|

||||

SSE (Streaming SIMD extensions)

|

||||

SSE2 (Streaming SIMD extensions 2)

|

||||

SS (Self-snoop)

|

||||

HTT (Multi-threading)

|

||||

TM (Thermal monitor supported)

|

||||

PBE (Pending break enabled)

|

||||

Version: Intel(R) Core(TM)2 Duo CPU P8600 @ 2.40GHz

|

||||

Voltage: 1.2 V

|

||||

External Clock: 266 MHz

|

||||

Max Speed: 2400 MHz

|

||||

Current Speed: 2400 MHz

|

||||

Status: Populated, Enabled

|

||||

Upgrade: None

|

||||

L1 Cache Handle: 0x000A

|

||||

L2 Cache Handle: 0x000C

|

||||

L3 Cache Handle: Not Provided

|

||||

Serial Number: Not Specified

|

||||

Asset Tag: Not Specified

|

||||

Part Number: Not Specified

|

||||

|

||||

Handle 0x0007, DMI type 5, 20 bytes

|

||||

Memory Controller Information

|

||||

Error Detecting Method: None

|

||||

Error Correcting Capabilities:

|

||||

None

|

||||

Supported Interleave: One-way Interleave

|

||||

Current Interleave: One-way Interleave

|

||||

Maximum Memory Module Size: 4096 MB

|

||||

Maximum Total Memory Size: 8192 MB

|

||||

Supported Speeds:

|

||||

Other

|

||||

Supported Memory Types:

|

||||

DIMM

|

||||

SDRAM

|

||||

Memory Module Voltage: 2.9 V

|

||||

Associated Memory Slots: 2

|

||||

0x0008

|

||||

0x0009

|

||||

Enabled Error Correcting Capabilities:

|

||||

Unknown

|

||||

|

||||

Handle 0x0008, DMI type 6, 12 bytes

|

||||

Memory Module Information

|

||||

Socket Designation: DIMM Slot 1

|

||||

Bank Connections: 0 1

|

||||

Current Speed: 42 ns

|

||||

Type: DIMM SDRAM

|

||||

Installed Size: 2048 MB (Double-bank Connection)

|

||||

Enabled Size: 2048 MB (Double-bank Connection)

|

||||

Error Status: OK

|

||||

|

||||

Handle 0x0009, DMI type 6, 12 bytes

|

||||

Memory Module Information

|

||||

Socket Designation: DIMM Slot 2

|

||||

Bank Connections: 2 3

|

||||

Current Speed: 42 ns

|

||||

Type: DIMM SDRAM

|

||||

Installed Size: Not Installed

|

||||

Enabled Size: Not Installed

|

||||

Error Status: OK

|

||||

|

||||

Handle 0x000A, DMI type 7, 19 bytes

|

||||

Cache Information

|

||||

Socket Designation: Internal L1 Cache

|

||||

Configuration: Enabled, Socketed, Level 1

|

||||

Operational Mode: Write Back

|

||||

Location: Internal

|

||||

Installed Size: 64 kB

|

||||

Maximum Size: 64 kB

|

||||

Supported SRAM Types:

|

||||

Synchronous

|

||||

Installed SRAM Type: Synchronous

|

||||

Speed: Unknown

|

||||

Error Correction Type: Single-bit ECC

|

||||

System Type: Instruction

|

||||

Associativity: 8-way Set-associative

|

||||

|

||||

Handle 0x000B, DMI type 7, 19 bytes

|

||||

Cache Information

|

||||

Socket Designation: Internal L1 Cache

|

||||

Configuration: Enabled, Socketed, Level 1

|

||||

Operational Mode: Write Back

|

||||

Location: Internal

|

||||

Installed Size: 64 kB

|

||||

Maximum Size: 64 kB

|

||||

Supported SRAM Types:

|

||||

Synchronous

|

||||

Installed SRAM Type: Synchronous

|

||||

Speed: Unknown

|

||||

Error Correction Type: Single-bit ECC

|

||||

System Type: Data

|

||||

Associativity: 8-way Set-associative

|

||||

|

||||

Handle 0x000C, DMI type 7, 19 bytes

|

||||

Cache Information

|

||||

Socket Designation: Internal L2 Cache

|

||||

Configuration: Enabled, Socketed, Level 2

|

||||

Operational Mode: Write Back

|

||||

Location: Internal

|

||||

Installed Size: 3072 kB

|

||||

Maximum Size: 3072 kB

|

||||

Supported SRAM Types:

|

||||

Burst

|

||||

Installed SRAM Type: Burst

|

||||

Speed: Unknown

|

||||

Error Correction Type: Single-bit ECC

|

||||

System Type: Unified

|

||||

Associativity: 8-way Set-associative

|

||||

|

||||

Handle 0x000D, DMI type 8, 9 bytes

|

||||

Port Connector Information

|

||||

Internal Reference Designator: Not Available

|

||||

Internal Connector Type: None

|

||||

External Reference Designator: External Monitor

|

||||

External Connector Type: DB-15 female

|

||||

Port Type: Video Port

|

||||

|

||||

Handle 0x000E, DMI type 8, 9 bytes

|

||||

Port Connector Information

|

||||

Internal Reference Designator: Not Available

|

||||

Internal Connector Type: None

|

||||

External Reference Designator: Microphone Jack

|

||||

External Connector Type: Mini Jack (headphones)

|

||||

Port Type: Audio Port

|

||||

|

||||

Handle 0x000F, DMI type 8, 9 bytes

|

||||

Port Connector Information

|

||||

Internal Reference Designator: Not Available

|

||||

Internal Connector Type: None

|

||||

External Reference Designator: Headphone Jack

|

||||

External Connector Type: Mini Jack (headphones)

|

||||

Port Type: Audio Port

|

||||

|

||||

Handle 0x0010, DMI type 8, 9 bytes

|

||||

Port Connector Information

|

||||

Internal Reference Designator: Not Available

|

||||

Internal Connector Type: None

|

||||

External Reference Designator: Modem

|

||||

External Connector Type: RJ-11

|

||||

Port Type: Modem Port

|

||||

|

||||

Handle 0x0011, DMI type 8, 9 bytes

|

||||

Port Connector Information

|

||||

Internal Reference Designator: Not Available

|

||||

Internal Connector Type: None

|

||||

External Reference Designator: Ethernet

|

||||

External Connector Type: RJ-45

|

||||

Port Type: Network Port

|

||||

|

||||

Handle 0x0012, DMI type 8, 9 bytes

|

||||

Port Connector Information

|

||||

Internal Reference Designator: Not Available

|

||||

Internal Connector Type: None

|

||||

External Reference Designator: USB 1

|

||||

External Connector Type: Access Bus (USB)

|

||||

Port Type: USB

|

||||

|

||||

Handle 0x0013, DMI type 8, 9 bytes

|

||||

Port Connector Information

|

||||

Internal Reference Designator: Not Available

|

||||

Internal Connector Type: None

|

||||

External Reference Designator: USB 2

|

||||

External Connector Type: Access Bus (USB)

|

||||

Port Type: USB

|

||||

|

||||

Handle 0x0014, DMI type 8, 9 bytes

|

||||

Port Connector Information

|

||||

Internal Reference Designator: Not Available

|

||||

Internal Connector Type: None

|

||||

External Reference Designator: USB 3

|

||||

External Connector Type: Access Bus (USB)

|

||||

Port Type: USB

|

||||

|

||||

Handle 0x0015, DMI type 126, 9 bytes

|

||||

Inactive

|

||||

|

||||

Handle 0x0016, DMI type 126, 9 bytes

|

||||

Inactive

|

||||

|

||||

Handle 0x0017, DMI type 126, 9 bytes

|

||||

Inactive

|

||||

|

||||

Handle 0x0018, DMI type 126, 9 bytes

|

||||

Inactive

|

||||

|

||||

Handle 0x0019, DMI type 126, 9 bytes

|

||||

Inactive

|

||||

|

||||

Handle 0x001A, DMI type 126, 9 bytes

|

||||

Inactive

|

||||

|

||||

Handle 0x001B, DMI type 126, 13 bytes

|

||||

Inactive

|

||||

|

||||

Handle 0x001C, DMI type 10, 6 bytes

|

||||

On Board Device Information

|

||||

Type: Other

|

||||

Status: Disabled

|

||||

Description: IBM Embedded Security hardware

|

||||

|

||||

Handle 0x001D, DMI type 11, 5 bytes

|

||||

OEM Strings

|

||||

String 1: IBM ThinkPad Embedded Controller -[7XHT24WW-1.06 ]-

|

||||

|

||||

Handle 0x001E, DMI type 13, 22 bytes

|

||||

BIOS Language Information

|

||||

Language Description Format: Abbreviated

|

||||

Installable Languages: 1

|

||||

enUS

|

||||

Currently Installed Language: enUS

|

||||

|

||||

Handle 0x001F, DMI type 15, 25 bytes

|

||||

System Event Log

|

||||

Area Length: 0 bytes

|

||||

Header Start Offset: 0x0000

|

||||

Header Length: 16 bytes

|

||||

Data Start Offset: 0x0010

|

||||

Access Method: General-purpose non-volatile data functions

|

||||

Access Address: 0x0000

|

||||

Status: Valid, Not Full

|

||||

Change Token: 0x000000FC

|

||||

Header Format: Type 1

|

||||

Supported Log Type Descriptors: 1

|

||||

Descriptor 1: POST error

|

||||

Data Format 1: POST results bitmap

|

||||

|

||||

Handle 0x0020, DMI type 16, 15 bytes

|

||||

Physical Memory Array

|

||||

Location: System Board Or Motherboard

|

||||

Use: System Memory

|

||||

Error Correction Type: None

|

||||

Maximum Capacity: 4 GB

|

||||

Error Information Handle: Not Provided

|

||||

Number Of Devices: 2

|

||||

|

||||

Handle 0x0021, DMI type 17, 27 bytes

|

||||

Memory Device

|

||||

Array Handle: 0x0020

|

||||

Error Information Handle: No Error

|

||||

Total Width: 64 bits

|

||||

Data Width: 64 bits

|

||||

Size: 2048 MB

|

||||

Form Factor: SODIMM

|

||||

Set: None

|

||||

Locator: DIMM 1

|

||||

Bank Locator: Bank 0/1

|

||||

Type: DDR3

|

||||

Type Detail: Synchronous

|

||||

Speed: 1066 MHz

|

||||

Manufacturer: 02FE

|

||||

Serial Number: F4BB7CA2

|

||||

Asset Tag: 0839

|

||||

Part Number: EBJ21UE8BASA-AE-E

|

||||

|

||||

Handle 0x0022, DMI type 17, 27 bytes

|

||||

Memory Device

|

||||

Array Handle: 0x0020

|

||||

Error Information Handle: No Error

|

||||

Total Width: Unknown

|

||||

Data Width: Unknown

|

||||

Size: No Module Installed

|

||||

Form Factor: SODIMM

|

||||

Set: None

|

||||

Locator: DIMM 2

|

||||

Bank Locator: Bank 2/3

|

||||

Type: DDR2

|

||||

Type Detail: Synchronous

|

||||

Speed: 1066 MHz

|

||||

Manufacturer:

|

||||

Serial Number:

|

||||

Asset Tag:

|

||||

Part Number:

|

||||

|

||||

Handle 0x0023, DMI type 18, 23 bytes

|

||||

32-bit Memory Error Information

|

||||

Type: OK

|

||||

Granularity: Unknown

|

||||

Operation: Unknown

|

||||

Vendor Syndrome: Unknown

|

||||

Memory Array Address: Unknown

|

||||

Device Address: Unknown

|

||||

Resolution: Unknown

|

||||

|

||||

Handle 0x0024, DMI type 19, 15 bytes

|

||||

Memory Array Mapped Address

|

||||

Starting Address: 0x00000000000

|

||||

Ending Address: 0x0007FFFFFFF

|

||||

Range Size: 2 GB

|

||||

Physical Array Handle: 0x0020

|

||||

Partition Width: 2

|

||||

|

||||

Handle 0x0025, DMI type 20, 19 bytes

|

||||

Memory Device Mapped Address

|

||||

Starting Address: 0x00000000000

|

||||

Ending Address: 0x0007FFFFFFF

|

||||

Range Size: 2 GB

|

||||

Physical Device Handle: 0x0021

|

||||

Memory Array Mapped Address Handle: 0x0024

|

||||

Partition Row Position: 1

|

||||

|

||||

Handle 0x0026, DMI type 20, 19 bytes

|

||||

Memory Device Mapped Address

|

||||

Starting Address: 0x0007FFFFC00

|

||||

Ending Address: 0x0007FFFFFFF

|

||||

Range Size: 1 kB

|

||||

Physical Device Handle: 0x0022

|

||||

Memory Array Mapped Address Handle: 0x0024

|

||||

Partition Row Position: 1

|

||||

|

||||

Handle 0x0027, DMI type 21, 7 bytes

|

||||

Built-in Pointing Device

|

||||

Type: Track Point

|

||||

Interface: PS/2

|

||||

Buttons: 3

|

||||

|

||||

Handle 0x0028, DMI type 126, 26 bytes

|

||||

Inactive

|

||||

|

||||

Handle 0x0029, DMI type 126, 26 bytes

|

||||

Inactive

|

||||

|

||||

Handle 0x002A, DMI type 24, 5 bytes

|

||||

Hardware Security

|

||||

Power-On Password Status: Disabled

|

||||

Keyboard Password Status: Disabled

|

||||

Administrator Password Status: Disabled

|

||||

Front Panel Reset Status: Unknown

|

||||

|

||||

Handle 0x002B, DMI type 32, 11 bytes

|

||||

System Boot Information

|

||||

Status: No errors detected

|

||||

|

||||

Handle 0x002C, DMI type 131, 17 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

83 11 2C 00 01 02 03 FF FF 1F 00 00 00 00 00 02

|

||||

00

|

||||

Strings:

|

||||

BOOTINF 20h

|

||||

BOOTDEV 21h

|

||||

KEYPTRS 23h

|

||||

|

||||

Handle 0x002D, DMI type 131, 22 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

83 16 2D 00 01 00 00 00 00 00 00 00 00 00 00 00

|

||||

00 00 00 00 00 01

|

||||

Strings:

|

||||

TVT-Enablement

|

||||

|

||||

Handle 0x002E, DMI type 132, 7 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

84 07 2E 00 02 D8 36

|

||||

|

||||

Handle 0x002F, DMI type 133, 5 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

85 05 2F 00 01

|

||||

Strings:

|

||||

KHOIHGIUCCHHII

|

||||

|

||||

Handle 0x0030, DMI type 134, 13 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

86 0D 30 00 30 10 08 20 00 00 00 00 00

|

||||

|

||||

Handle 0x0031, DMI type 134, 16 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

86 10 31 00 00 49 4E 54 43 01 01 00 00 02 01 02

|

||||

Strings:

|

||||

TPM INFO

|

||||

System Reserved

|

||||

|

||||

Handle 0x0032, DMI type 135, 13 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

87 0D 32 00 54 50 07 00 01 00 00 00 00

|

||||

|

||||

Handle 0x0033, DMI type 135, 18 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

87 12 33 00 54 50 07 01 01 B9 05 00 00 00 00 00

|

||||

00 00

|

||||

|

||||

Handle 0x0034, DMI type 135, 35 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

87 23 34 00 54 50 07 02 42 41 59 20 49 2F 4F 20

|

||||

01 00 02 00 00 0B 00 48 1C 3E 18 02 00 0B 00 40

|

||||

1C 3A 18

|

||||

|

||||

Handle 0x0035, DMI type 135, 34 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

87 22 35 00 54 50 07 04 01 06 01 01 02 00 02 01

|

||||

02 00 03 01 02 00 04 01 02 00 05 01 02 00 06 01

|

||||

02 00

|

||||

|

||||

Handle 0x0036, DMI type 135, 10 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

87 0A 36 00 54 50 07 03 01 0A

|

||||

|

||||

Handle 0x0037, DMI type 136, 6 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

88 06 37 00 5A 5A

|

||||

|

||||

Handle 0x0038, DMI type 126, 28 bytes

|

||||

Inactive

|

||||

|

||||

Handle 0x0039, DMI type 138, 40 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

8A 28 39 00 14 01 02 01 40 02 01 40 02 01 40 02

|

||||

01 40 01 40 42 49 4F 53 20 50 61 73 73 77 6F 72

|

||||

64 20 46 6F 72 6D 61 74

|

||||

|

||||

Handle 0x003A, DMI type 139, 37 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

8B 25 3A 00 11 01 0A 00 00 00 00 00 00 00 00 00

|

||||

00 50 57 4D 53 20 4B 65 79 20 49 6E 66 6F 72 6D

|

||||

61 74 69 6F 6E

|

||||

|

||||

Handle 0x003B, DMI type 140, 67 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

8C 43 3B 00 4C 45 4E 4F 56 4F 0B 00 01 9A 13 CD

|

||||

C4 7A 2A 8E 76 C3 C4 4E B9 B1 DD 4E 7C 01 00 00

|

||||

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

|

||||

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

|

||||

00 00 00

|

||||

|

||||

Handle 0x003C, DMI type 140, 47 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

8C 2F 3C 00 4C 45 4E 4F 56 4F 0B 01 01 08 00 BF

|

||||

DA 3C 04 5C 72 D9 7D 0D 79 DE 46 98 23 10 B1 00

|

||||

00 00 00 10 00 10 00 10 01 D0 00 20 01 00 01

|

||||

|

||||

Handle 0x003D, DMI type 140, 63 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

8C 3F 3D 00 4C 45 4E 4F 56 4F 0B 02 01 00 00 00

|

||||

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

|

||||

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

|

||||

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

|

||||

|

||||

Handle 0x003E, DMI type 140, 17 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

8C 11 3E 00 4C 45 4E 4F 56 4F 0B 03 01 00 00 00

|

||||

00

|

||||

|

||||

Handle 0x003F, DMI type 140, 19 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

8C 13 3F 00 4C 45 4E 4F 56 4F 0B 04 01 B2 00 53

|

||||

4D 20 00

|

||||

|

||||

Handle 0x0040, DMI type 129, 8 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

81 08 40 00 01 01 02 01

|

||||

Strings:

|

||||

Intel_ASF

|

||||

Intel_ASF_001

|

||||

|

||||

Handle 0x0041, DMI type 130, 20 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

82 14 41 00 24 41 4D 54 01 01 01 01 01 A5 0B 04

|

||||

00 00 00 00

|

||||

|

||||

Handle 0x0042, DMI type 131, 64 bytes

|

||||

OEM-specific Type

|

||||

Header and Data:

|

||||

83 40 42 00 14 00 00 00 00 00 40 2A 00 00 00 00

|

||||

F8 00 17 29 00 00 00 00 2D 00 00 00 00 00 04 00

|

||||

64 04 03 00 01 00 01 15 C8 00 F5 10 00 00 00 00

|

||||

00 00 00 00 07 00 00 00 76 50 72 6F 00 00 00 00

|

||||

|

||||

Handle 0x0043, DMI type 127, 4 bytes

|

||||

End Of Table

|

||||

|

||||

|

|

@ -1 +0,0 @@

|

|||

bash: ectool: command not found

|

||||

|

|

@ -1,14 +0,0 @@

|

|||

========================================================================

|

||||

WARNING! You seem to be running flashrom on an unsupported laptop.

|

||||

Laptops, notebooks and netbooks are difficult to support and we

|

||||

recommend to use the vendor flashing utility. The embedded controller

|

||||

(EC) in these machines often interacts badly with flashing.

|

||||

See http://www.flashrom.org/Laptops for details.

|

||||

|

||||

If flash is shared with the EC, erase is guaranteed to brick your laptop

|

||||

and write may brick your laptop.

|

||||

Read and probe may irritate your EC and cause fan failure, backlight

|

||||

failure and sudden poweroff.

|

||||

You have been warned.

|

||||

========================================================================

|

||||

Proceeding anyway because user forced us to.

|

||||

|

|

@ -1,289 +0,0 @@

|

|||

flashrom v0.9.6.1-r1563 on GNU+Linux 3.13.0-39-lowlatency (x86_64)

|

||||

flashrom is free software, get the source code at http://www.flashrom.org

|

||||

|

||||

flashrom was built with libpci 3.1.9, GCC 4.7.1, little endian

|

||||

Command line (3 args): flashrom -V -p internal:laptop=force_I_want_a_brick

|

||||

Calibrating delay loop... OS timer resolution is 1 usecs, 1578M loops per second, 10 myus = 11 us, 100 myus = 114 us, 1000 myus = 1002 us, 10000 myus = 10004 us, 4 myus = 5 us, OK.

|

||||

Initializing internal programmer

|

||||

No coreboot table found.

|

||||

DMI string system-manufacturer: "LENOVO"

|

||||

DMI string system-product-name: "7459GW4"

|

||||

DMI string system-version: "ThinkPad X200"

|

||||

DMI string baseboard-manufacturer: "LENOVO"

|

||||

DMI string baseboard-product-name: "7459GW4"

|

||||

DMI string baseboard-version: "Not Available"

|

||||

DMI string chassis-type: "Notebook"

|

||||

Laptop detected via DMI.

|

||||

Found chipset "Intel ICH9M-E" with PCI ID 8086:2917. Enabling flash write...

|

||||

0xfff80000/0xffb80000 FWH IDSEL: 0x0

|

||||

0xfff00000/0xffb00000 FWH IDSEL: 0x0

|

||||

0xffe80000/0xffa80000 FWH IDSEL: 0x0

|

||||

0xffe00000/0xffa00000 FWH IDSEL: 0x0

|

||||

0xffd80000/0xff980000 FWH IDSEL: 0x0

|

||||

0xffd00000/0xff900000 FWH IDSEL: 0x0

|

||||

0xffc80000/0xff880000 FWH IDSEL: 0x0

|

||||

0xffc00000/0xff800000 FWH IDSEL: 0x0

|

||||

0xff700000/0xff300000 FWH IDSEL: 0x4

|

||||

0xff600000/0xff200000 FWH IDSEL: 0x5

|

||||

0xff500000/0xff100000 FWH IDSEL: 0x6

|

||||

0xff400000/0xff000000 FWH IDSEL: 0x7

|

||||

0xfff80000/0xffb80000 FWH decode enabled

|

||||

0xfff00000/0xffb00000 FWH decode enabled

|

||||

0xffe80000/0xffa80000 FWH decode enabled

|

||||

0xffe00000/0xffa00000 FWH decode enabled

|

||||

0xffd80000/0xff980000 FWH decode enabled

|

||||

0xffd00000/0xff900000 FWH decode enabled

|

||||

0xffc80000/0xff880000 FWH decode enabled

|

||||

0xffc00000/0xff800000 FWH decode enabled

|

||||

0xff700000/0xff300000 FWH decode disabled

|

||||

0xff600000/0xff200000 FWH decode disabled

|

||||

0xff500000/0xff100000 FWH decode disabled

|

||||

0xff400000/0xff000000 FWH decode disabled

|

||||

Maximum FWH chip size: 0x400000 bytes

|

||||

BIOS Lock Enable: disabled, BIOS Write Enable: disabled, BIOS_CNTL is 0x0

|

||||

Root Complex Register Block address = 0xfed1c000

|

||||

GCS = 0x7b0461: BIOS Interface Lock-Down: enabled, Boot BIOS Straps: 0x1 (SPI)

|

||||

Top Swap : not enabled

|

||||

SPIBAR = 0xfed1c000 + 0x3800

|

||||

0x04: 0xe008 (HSFS)

|

||||

HSFS: FDONE=0, FCERR=0, AEL=0, BERASE=1, SCIP=0, FDOPSS=1, FDV=1, FLOCKDN=1

|

||||

WARNING: SPI Configuration Lockdown activated.

|

||||

Reading OPCODES... done

|

||||

0x06: 0x3f04 (HSFC)

|

||||

HSFC: FGO=0, FCYCLE=2, FDBC=63, SME=0

|

||||

0x08: 0x00001000 (FADDR)

|

||||

0x50: 0x00001a1b (FRAP)

|

||||

BMWAG 0x00, BMRAG 0x00, BRWA 0x1a, BRRA 0x1b

|

||||

0x54: 0x00000000 FREG0: WARNING: Flash Descriptor region (0x00000000-0x00000fff) is read-only.

|

||||

0x58: 0x07ff0600 FREG1: BIOS region (0x00600000-0x007fffff) is read-write.

|

||||

0x5C: 0x05f50001 FREG2: WARNING: Management Engine region (0x00001000-0x005f5fff) is locked.

|

||||

0x60: 0x05f705f6 FREG3: Gigabit Ethernet region (0x005f6000-0x005f7fff) is read-write.

|

||||

0x64: 0x05ff05f8 FREG4: Platform Data region (0x005f8000-0x005fffff) is read-write.

|

||||

0x74: 0x9fff07e0 PR0: WARNING: 0x007e0000-0x01ffffff is read-only.

|

||||

0x84: 0x85ff85f8 PR4: WARNING: 0x005f8000-0x005fffff is locked.

|

||||

Please send a verbose log to flashrom@flashrom.org if this board is not listed on

|

||||

http://flashrom.org/Supported_hardware#Supported_mainboards yet.

|

||||

Writes have been disabled. You can enforce write support with the

|

||||

ich_spi_force programmer option, but it will most likely harm your hardware!

|

||||

If you force flashrom you will get no support if something breaks.

|

||||

0x90: 0x04 (SSFS)

|

||||

SSFS: SCIP=0, FDONE=1, FCERR=0, AEL=0

|

||||

0x91: 0x000000 (SSFC)

|

||||

SSFC: SCGO=0, ACS=0, SPOP=0, COP=0, DBC=0, SME=0, SCF=0

|

||||

0x94: 0x5006 (PREOP)

|

||||

0x96: 0x143b (OPTYPE)

|

||||

0x98: 0x05200302 (OPMENU)

|

||||

0x9C: 0x0601209f (OPMENU+4)

|

||||

0xA0: 0x00000000 (BBAR)

|

||||

0xC4: 0x00002005 (LVSCC)

|

||||

LVSCC: BES=0x1, WG=1, WSR=0, WEWS=0, EO=0x20, VCL=0

|

||||

0xC8: 0x00002005 (UVSCC)

|

||||

UVSCC: BES=0x1, WG=1, WSR=0, WEWS=0, EO=0x20, VCL=0

|

||||

0xD0: 0x00000000 (FPB)

|

||||

|

||||

SPI Read Configuration: prefetching disabled, caching enabled, OK.

|

||||

The following protocols are supported: FWH, SPI.

|

||||

Probing for AMIC A25L05PT, 64 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for AMIC A25L05PU, 64 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for AMIC A25L10PT, 128 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for AMIC A25L10PU, 128 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for AMIC A25L20PT, 256 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for AMIC A25L20PU, 256 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for AMIC A25L40PT, 512 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for AMIC A25L40PU, 512 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for AMIC A25L80P, 1024 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for AMIC A25L16PT, 2048 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for AMIC A25L16PU, 2048 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for AMIC A25L512, 64 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for AMIC A25L010, 128 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for AMIC A25L020, 256 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for AMIC A25L040, 512 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for AMIC A25L080, 1024 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for AMIC A25L016, 2048 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for AMIC A25L032, 4096 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for AMIC A25LQ032, 4096 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT25DF021, 256 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT25DF041A, 512 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT25DF081, 1024 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT25DF081A, 1024 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT25DF161, 2048 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT25DF321, 4096 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT25DF321A, 4096 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT25DF641(A), 8192 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT25DQ161, 2048 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT25F512B, 64 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT25FS010, 128 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT25FS040, 512 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT26DF041, 512 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT26DF081A, 1024 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT26DF161, 2048 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT26DF161A, 2048 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT26F004, 512 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT45CS1282, 16896 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT45DB011D, 128 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT45DB021D, 256 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT45DB041D, 512 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT45DB081D, 1024 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT45DB161D, 2048 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT45DB321C, 4224 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT45DB321D, 4096 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Atmel AT45DB642D, 8192 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for EMST F25L008A, 1024 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25B05, 64 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25B05T, 64 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25B10, 128 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25B10T, 128 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25B20, 256 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25B20T, 256 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25B40, 512 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25B40T, 512 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25B80, 1024 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25B80T, 1024 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25B16, 2048 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25B16T, 2048 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25B32, 4096 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25B32T, 4096 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25B64, 8192 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25B64T, 8192 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25F05, 64 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25F10, 128 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25F20, 256 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25F40, 512 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25F80, 1024 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||

Probing for Eon EN25F16, 2048 kB: probe_spi_rdid_generic: id1 0xc2, id2 0x2017

|

||||