Censored Libreboot 20230710 website

Signed-off-by: Leah Rowe <leah@libreboot.org>master

commit

6a52fb9f57

|

|

@ -0,0 +1,8 @@

|

|||

*.html

|

||||

/site/news/index*

|

||||

/site/sitemap.md

|

||||

/site/push

|

||||

*feed.xml

|

||||

*.sha1sum

|

||||

*.hash

|

||||

*.date

|

||||

|

|

@ -0,0 +1,5 @@

|

|||

TITLE="-T Censored-libreboot"

|

||||

DOMAIN="https://censored.libreboot.org/"

|

||||

BLOGDIR="news/" # leave as empty string if you want the blog to be the homepage

|

||||

CSS="--css /global.css"

|

||||

LAZY="y"

|

||||

|

|

@ -0,0 +1,451 @@

|

|||

|

||||

GNU Free Documentation License

|

||||

Version 1.3, 3 November 2008

|

||||

|

||||

|

||||

Copyright (C) 2000, 2001, 2002, 2007, 2008 Free Software Foundation, Inc.

|

||||

<https://fsf.org/>

|

||||

Everyone is permitted to copy and distribute verbatim copies

|

||||

of this license document, but changing it is not allowed.

|

||||

|

||||

0. PREAMBLE

|

||||

|

||||

The purpose of this License is to make a manual, textbook, or other

|

||||

functional and useful document "free" in the sense of freedom: to

|

||||

assure everyone the effective freedom to copy and redistribute it,

|

||||

with or without modifying it, either commercially or noncommercially.

|

||||

Secondarily, this License preserves for the author and publisher a way

|

||||

to get credit for their work, while not being considered responsible

|

||||

for modifications made by others.

|

||||

|

||||

This License is a kind of "copyleft", which means that derivative

|

||||

works of the document must themselves be free in the same sense. It

|

||||

complements the GNU General Public License, which is a copyleft

|

||||

license designed for free software.

|

||||

|

||||

We have designed this License in order to use it for manuals for free

|

||||

software, because free software needs free documentation: a free

|

||||

program should come with manuals providing the same freedoms that the

|

||||

software does. But this License is not limited to software manuals;

|

||||

it can be used for any textual work, regardless of subject matter or

|

||||

whether it is published as a printed book. We recommend this License

|

||||

principally for works whose purpose is instruction or reference.

|

||||

|

||||

|

||||

1. APPLICABILITY AND DEFINITIONS

|

||||

|

||||

This License applies to any manual or other work, in any medium, that

|

||||

contains a notice placed by the copyright holder saying it can be

|

||||

distributed under the terms of this License. Such a notice grants a

|

||||

world-wide, royalty-free license, unlimited in duration, to use that

|

||||

work under the conditions stated herein. The "Document", below,

|

||||

refers to any such manual or work. Any member of the public is a

|

||||

licensee, and is addressed as "you". You accept the license if you

|

||||

copy, modify or distribute the work in a way requiring permission

|

||||

under copyright law.

|

||||

|

||||

A "Modified Version" of the Document means any work containing the

|

||||

Document or a portion of it, either copied verbatim, or with

|

||||

modifications and/or translated into another language.

|

||||

|

||||

A "Secondary Section" is a named appendix or a front-matter section of

|

||||

the Document that deals exclusively with the relationship of the

|

||||

publishers or authors of the Document to the Document's overall

|

||||

subject (or to related matters) and contains nothing that could fall

|

||||

directly within that overall subject. (Thus, if the Document is in

|

||||

part a textbook of mathematics, a Secondary Section may not explain

|

||||

any mathematics.) The relationship could be a matter of historical

|

||||

connection with the subject or with related matters, or of legal,

|

||||

commercial, philosophical, ethical or political position regarding

|

||||

them.

|

||||

|

||||

The "Invariant Sections" are certain Secondary Sections whose titles

|

||||

are designated, as being those of Invariant Sections, in the notice

|

||||

that says that the Document is released under this License. If a

|

||||

section does not fit the above definition of Secondary then it is not

|

||||

allowed to be designated as Invariant. The Document may contain zero

|

||||

Invariant Sections. If the Document does not identify any Invariant

|

||||

Sections then there are none.

|

||||

|

||||

The "Cover Texts" are certain short passages of text that are listed,

|

||||

as Front-Cover Texts or Back-Cover Texts, in the notice that says that

|

||||

the Document is released under this License. A Front-Cover Text may

|

||||

be at most 5 words, and a Back-Cover Text may be at most 25 words.

|

||||

|

||||

A "Transparent" copy of the Document means a machine-readable copy,

|

||||

represented in a format whose specification is available to the

|

||||

general public, that is suitable for revising the document

|

||||

straightforwardly with generic text editors or (for images composed of

|

||||

pixels) generic paint programs or (for drawings) some widely available

|

||||

drawing editor, and that is suitable for input to text formatters or

|

||||

for automatic translation to a variety of formats suitable for input

|

||||

to text formatters. A copy made in an otherwise Transparent file

|

||||

format whose markup, or absence of markup, has been arranged to thwart

|

||||

or discourage subsequent modification by readers is not Transparent.

|

||||

An image format is not Transparent if used for any substantial amount

|

||||

of text. A copy that is not "Transparent" is called "Opaque".

|

||||

|

||||

Examples of suitable formats for Transparent copies include plain

|

||||

ASCII without markup, Texinfo input format, LaTeX input format, SGML

|

||||

or XML using a publicly available DTD, and standard-conforming simple

|

||||

HTML, PostScript or PDF designed for human modification. Examples of

|

||||

transparent image formats include PNG, XCF and JPG. Opaque formats

|

||||

include proprietary formats that can be read and edited only by

|

||||

proprietary word processors, SGML or XML for which the DTD and/or

|

||||

processing tools are not generally available, and the

|

||||

machine-generated HTML, PostScript or PDF produced by some word

|

||||

processors for output purposes only.

|

||||

|

||||

The "Title Page" means, for a printed book, the title page itself,

|

||||

plus such following pages as are needed to hold, legibly, the material

|

||||

this License requires to appear in the title page. For works in

|

||||

formats which do not have any title page as such, "Title Page" means

|

||||

the text near the most prominent appearance of the work's title,

|

||||

preceding the beginning of the body of the text.

|

||||

|

||||

The "publisher" means any person or entity that distributes copies of

|

||||

the Document to the public.

|

||||

|

||||

A section "Entitled XYZ" means a named subunit of the Document whose

|

||||

title either is precisely XYZ or contains XYZ in parentheses following

|

||||

text that translates XYZ in another language. (Here XYZ stands for a

|

||||

specific section name mentioned below, such as "Acknowledgements",

|

||||

"Dedications", "Endorsements", or "History".) To "Preserve the Title"

|

||||

of such a section when you modify the Document means that it remains a

|

||||

section "Entitled XYZ" according to this definition.

|

||||

|

||||

The Document may include Warranty Disclaimers next to the notice which

|

||||

states that this License applies to the Document. These Warranty

|

||||

Disclaimers are considered to be included by reference in this

|

||||

License, but only as regards disclaiming warranties: any other

|

||||

implication that these Warranty Disclaimers may have is void and has

|

||||

no effect on the meaning of this License.

|

||||

|

||||

2. VERBATIM COPYING

|

||||

|

||||

You may copy and distribute the Document in any medium, either

|

||||

commercially or noncommercially, provided that this License, the

|

||||

copyright notices, and the license notice saying this License applies

|

||||

to the Document are reproduced in all copies, and that you add no

|

||||

other conditions whatsoever to those of this License. You may not use

|

||||

technical measures to obstruct or control the reading or further

|

||||

copying of the copies you make or distribute. However, you may accept

|

||||

compensation in exchange for copies. If you distribute a large enough

|

||||

number of copies you must also follow the conditions in section 3.

|

||||

|

||||

You may also lend copies, under the same conditions stated above, and

|

||||

you may publicly display copies.

|

||||

|

||||

|

||||

3. COPYING IN QUANTITY

|

||||

|

||||

If you publish printed copies (or copies in media that commonly have

|

||||

printed covers) of the Document, numbering more than 100, and the

|

||||

Document's license notice requires Cover Texts, you must enclose the

|

||||

copies in covers that carry, clearly and legibly, all these Cover

|

||||

Texts: Front-Cover Texts on the front cover, and Back-Cover Texts on

|

||||

the back cover. Both covers must also clearly and legibly identify

|

||||

you as the publisher of these copies. The front cover must present

|

||||

the full title with all words of the title equally prominent and

|

||||

visible. You may add other material on the covers in addition.

|

||||

Copying with changes limited to the covers, as long as they preserve

|

||||

the title of the Document and satisfy these conditions, can be treated

|

||||

as verbatim copying in other respects.

|

||||

|

||||

If the required texts for either cover are too voluminous to fit

|

||||

legibly, you should put the first ones listed (as many as fit

|

||||

reasonably) on the actual cover, and continue the rest onto adjacent

|

||||

pages.

|

||||

|

||||

If you publish or distribute Opaque copies of the Document numbering

|

||||

more than 100, you must either include a machine-readable Transparent

|

||||

copy along with each Opaque copy, or state in or with each Opaque copy

|

||||

a computer-network location from which the general network-using

|

||||

public has access to download using public-standard network protocols

|

||||

a complete Transparent copy of the Document, free of added material.

|

||||

If you use the latter option, you must take reasonably prudent steps,

|

||||

when you begin distribution of Opaque copies in quantity, to ensure

|

||||

that this Transparent copy will remain thus accessible at the stated

|

||||

location until at least one year after the last time you distribute an

|

||||

Opaque copy (directly or through your agents or retailers) of that

|

||||

edition to the public.

|

||||

|

||||

It is requested, but not required, that you contact the authors of the

|

||||

Document well before redistributing any large number of copies, to

|

||||

give them a chance to provide you with an updated version of the

|

||||

Document.

|

||||

|

||||

|

||||

4. MODIFICATIONS

|

||||

|

||||

You may copy and distribute a Modified Version of the Document under

|

||||

the conditions of sections 2 and 3 above, provided that you release

|

||||

the Modified Version under precisely this License, with the Modified

|

||||

Version filling the role of the Document, thus licensing distribution

|

||||

and modification of the Modified Version to whoever possesses a copy

|

||||

of it. In addition, you must do these things in the Modified Version:

|

||||

|

||||

A. Use in the Title Page (and on the covers, if any) a title distinct

|

||||

from that of the Document, and from those of previous versions

|

||||

(which should, if there were any, be listed in the History section

|

||||

of the Document). You may use the same title as a previous version

|

||||

if the original publisher of that version gives permission.

|

||||

B. List on the Title Page, as authors, one or more persons or entities

|

||||

responsible for authorship of the modifications in the Modified

|

||||

Version, together with at least five of the principal authors of the

|

||||

Document (all of its principal authors, if it has fewer than five),

|

||||

unless they release you from this requirement.

|

||||

C. State on the Title page the name of the publisher of the

|

||||

Modified Version, as the publisher.

|

||||

D. Preserve all the copyright notices of the Document.

|

||||

E. Add an appropriate copyright notice for your modifications

|

||||

adjacent to the other copyright notices.

|

||||

F. Include, immediately after the copyright notices, a license notice

|

||||

giving the public permission to use the Modified Version under the

|

||||

terms of this License, in the form shown in the Addendum below.

|

||||

G. Preserve in that license notice the full lists of Invariant Sections

|

||||

and required Cover Texts given in the Document's license notice.

|

||||

H. Include an unaltered copy of this License.

|

||||

I. Preserve the section Entitled "History", Preserve its Title, and add

|

||||

to it an item stating at least the title, year, new authors, and

|

||||

publisher of the Modified Version as given on the Title Page. If

|

||||

there is no section Entitled "History" in the Document, create one

|

||||

stating the title, year, authors, and publisher of the Document as

|

||||

given on its Title Page, then add an item describing the Modified

|

||||

Version as stated in the previous sentence.

|

||||

J. Preserve the network location, if any, given in the Document for

|

||||

public access to a Transparent copy of the Document, and likewise

|

||||

the network locations given in the Document for previous versions

|

||||

it was based on. These may be placed in the "History" section.

|

||||

You may omit a network location for a work that was published at

|

||||

least four years before the Document itself, or if the original

|

||||

publisher of the version it refers to gives permission.

|

||||

K. For any section Entitled "Acknowledgements" or "Dedications",

|

||||

Preserve the Title of the section, and preserve in the section all

|

||||

the substance and tone of each of the contributor acknowledgements

|

||||

and/or dedications given therein.

|

||||

L. Preserve all the Invariant Sections of the Document,

|

||||

unaltered in their text and in their titles. Section numbers

|

||||

or the equivalent are not considered part of the section titles.

|

||||

M. Delete any section Entitled "Endorsements". Such a section

|

||||

may not be included in the Modified Version.

|

||||

N. Do not retitle any existing section to be Entitled "Endorsements"

|

||||

or to conflict in title with any Invariant Section.

|

||||

O. Preserve any Warranty Disclaimers.

|

||||

|

||||

If the Modified Version includes new front-matter sections or

|

||||

appendices that qualify as Secondary Sections and contain no material

|

||||

copied from the Document, you may at your option designate some or all

|

||||

of these sections as invariant. To do this, add their titles to the

|

||||

list of Invariant Sections in the Modified Version's license notice.

|

||||

These titles must be distinct from any other section titles.

|

||||

|

||||

You may add a section Entitled "Endorsements", provided it contains

|

||||

nothing but endorsements of your Modified Version by various

|

||||

parties--for example, statements of peer review or that the text has

|

||||

been approved by an organization as the authoritative definition of a

|

||||

standard.

|

||||

|

||||

You may add a passage of up to five words as a Front-Cover Text, and a

|

||||

passage of up to 25 words as a Back-Cover Text, to the end of the list

|

||||

of Cover Texts in the Modified Version. Only one passage of

|

||||

Front-Cover Text and one of Back-Cover Text may be added by (or

|

||||

through arrangements made by) any one entity. If the Document already

|

||||

includes a cover text for the same cover, previously added by you or

|

||||

by arrangement made by the same entity you are acting on behalf of,

|

||||

you may not add another; but you may replace the old one, on explicit

|

||||

permission from the previous publisher that added the old one.

|

||||

|

||||

The author(s) and publisher(s) of the Document do not by this License

|

||||

give permission to use their names for publicity for or to assert or

|

||||

imply endorsement of any Modified Version.

|

||||

|

||||

|

||||

5. COMBINING DOCUMENTS

|

||||

|

||||

You may combine the Document with other documents released under this

|

||||

License, under the terms defined in section 4 above for modified

|

||||

versions, provided that you include in the combination all of the

|

||||

Invariant Sections of all of the original documents, unmodified, and

|

||||

list them all as Invariant Sections of your combined work in its

|

||||

license notice, and that you preserve all their Warranty Disclaimers.

|

||||

|

||||

The combined work need only contain one copy of this License, and

|

||||

multiple identical Invariant Sections may be replaced with a single

|

||||

copy. If there are multiple Invariant Sections with the same name but

|

||||

different contents, make the title of each such section unique by

|

||||

adding at the end of it, in parentheses, the name of the original

|

||||

author or publisher of that section if known, or else a unique number.

|

||||

Make the same adjustment to the section titles in the list of

|

||||

Invariant Sections in the license notice of the combined work.

|

||||

|

||||

In the combination, you must combine any sections Entitled "History"

|

||||

in the various original documents, forming one section Entitled

|

||||

"History"; likewise combine any sections Entitled "Acknowledgements",

|

||||

and any sections Entitled "Dedications". You must delete all sections

|

||||

Entitled "Endorsements".

|

||||

|

||||

|

||||

6. COLLECTIONS OF DOCUMENTS

|

||||

|

||||

You may make a collection consisting of the Document and other

|

||||

documents released under this License, and replace the individual

|

||||

copies of this License in the various documents with a single copy

|

||||

that is included in the collection, provided that you follow the rules

|

||||

of this License for verbatim copying of each of the documents in all

|

||||

other respects.

|

||||

|

||||

You may extract a single document from such a collection, and

|

||||

distribute it individually under this License, provided you insert a

|

||||

copy of this License into the extracted document, and follow this

|

||||

License in all other respects regarding verbatim copying of that

|

||||

document.

|

||||

|

||||

|

||||

7. AGGREGATION WITH INDEPENDENT WORKS

|

||||

|

||||

A compilation of the Document or its derivatives with other separate

|

||||

and independent documents or works, in or on a volume of a storage or

|

||||

distribution medium, is called an "aggregate" if the copyright

|

||||

resulting from the compilation is not used to limit the legal rights

|

||||

of the compilation's users beyond what the individual works permit.

|

||||

When the Document is included in an aggregate, this License does not

|

||||

apply to the other works in the aggregate which are not themselves

|

||||

derivative works of the Document.

|

||||

|

||||

If the Cover Text requirement of section 3 is applicable to these

|

||||

copies of the Document, then if the Document is less than one half of

|

||||

the entire aggregate, the Document's Cover Texts may be placed on

|

||||

covers that bracket the Document within the aggregate, or the

|

||||

electronic equivalent of covers if the Document is in electronic form.

|

||||

Otherwise they must appear on printed covers that bracket the whole

|

||||

aggregate.

|

||||

|

||||

|

||||

8. TRANSLATION

|

||||

|

||||

Translation is considered a kind of modification, so you may

|

||||

distribute translations of the Document under the terms of section 4.

|

||||

Replacing Invariant Sections with translations requires special

|

||||

permission from their copyright holders, but you may include

|

||||

translations of some or all Invariant Sections in addition to the

|

||||

original versions of these Invariant Sections. You may include a

|

||||

translation of this License, and all the license notices in the

|

||||

Document, and any Warranty Disclaimers, provided that you also include

|

||||

the original English version of this License and the original versions

|

||||

of those notices and disclaimers. In case of a disagreement between

|

||||

the translation and the original version of this License or a notice

|

||||

or disclaimer, the original version will prevail.

|

||||

|

||||

If a section in the Document is Entitled "Acknowledgements",

|

||||

"Dedications", or "History", the requirement (section 4) to Preserve

|

||||

its Title (section 1) will typically require changing the actual

|

||||

title.

|

||||

|

||||

|

||||

9. TERMINATION

|

||||

|

||||

You may not copy, modify, sublicense, or distribute the Document

|

||||

except as expressly provided under this License. Any attempt

|

||||

otherwise to copy, modify, sublicense, or distribute it is void, and

|

||||

will automatically terminate your rights under this License.

|

||||

|

||||

However, if you cease all violation of this License, then your license

|

||||

from a particular copyright holder is reinstated (a) provisionally,

|

||||

unless and until the copyright holder explicitly and finally

|

||||

terminates your license, and (b) permanently, if the copyright holder

|

||||

fails to notify you of the violation by some reasonable means prior to

|

||||

60 days after the cessation.

|

||||

|

||||

Moreover, your license from a particular copyright holder is

|

||||

reinstated permanently if the copyright holder notifies you of the

|

||||

violation by some reasonable means, this is the first time you have

|

||||

received notice of violation of this License (for any work) from that

|

||||

copyright holder, and you cure the violation prior to 30 days after

|

||||

your receipt of the notice.

|

||||

|

||||

Termination of your rights under this section does not terminate the

|

||||

licenses of parties who have received copies or rights from you under

|

||||

this License. If your rights have been terminated and not permanently

|

||||

reinstated, receipt of a copy of some or all of the same material does

|

||||

not give you any rights to use it.

|

||||

|

||||

|

||||

10. FUTURE REVISIONS OF THIS LICENSE

|

||||

|

||||

The Free Software Foundation may publish new, revised versions of the

|

||||

GNU Free Documentation License from time to time. Such new versions

|

||||

will be similar in spirit to the present version, but may differ in

|

||||

detail to address new problems or concerns. See

|

||||

https://www.gnu.org/licenses/.

|

||||

|

||||

Each version of the License is given a distinguishing version number.

|

||||

If the Document specifies that a particular numbered version of this

|

||||

License "or any later version" applies to it, you have the option of

|

||||

following the terms and conditions either of that specified version or

|

||||

of any later version that has been published (not as a draft) by the

|

||||

Free Software Foundation. If the Document does not specify a version

|

||||

number of this License, you may choose any version ever published (not

|

||||

as a draft) by the Free Software Foundation. If the Document

|

||||

specifies that a proxy can decide which future versions of this

|

||||

License can be used, that proxy's public statement of acceptance of a

|

||||

version permanently authorizes you to choose that version for the

|

||||

Document.

|

||||

|

||||

11. RELICENSING

|

||||

|

||||

"Massive Multiauthor Collaboration Site" (or "MMC Site") means any

|

||||

World Wide Web server that publishes copyrightable works and also

|

||||

provides prominent facilities for anybody to edit those works. A

|

||||

public wiki that anybody can edit is an example of such a server. A

|

||||

"Massive Multiauthor Collaboration" (or "MMC") contained in the site

|

||||

means any set of copyrightable works thus published on the MMC site.

|

||||

|

||||

"CC-BY-SA" means the Creative Commons Attribution-Share Alike 3.0

|

||||

license published by Creative Commons Corporation, a not-for-profit

|

||||

corporation with a principal place of business in San Francisco,

|

||||

California, as well as future copyleft versions of that license

|

||||

published by that same organization.

|

||||

|

||||

"Incorporate" means to publish or republish a Document, in whole or in

|

||||

part, as part of another Document.

|

||||

|

||||

An MMC is "eligible for relicensing" if it is licensed under this

|

||||

License, and if all works that were first published under this License

|

||||

somewhere other than this MMC, and subsequently incorporated in whole or

|

||||

in part into the MMC, (1) had no cover texts or invariant sections, and

|

||||

(2) were thus incorporated prior to November 1, 2008.

|

||||

|

||||

The operator of an MMC Site may republish an MMC contained in the site

|

||||

under CC-BY-SA on the same site at any time before August 1, 2009,

|

||||

provided the MMC is eligible for relicensing.

|

||||

|

||||

|

||||

ADDENDUM: How to use this License for your documents

|

||||

|

||||

To use this License in a document you have written, include a copy of

|

||||

the License in the document and put the following copyright and

|

||||

license notices just after the title page:

|

||||

|

||||

Copyright (c) YEAR YOUR NAME.

|

||||

Permission is granted to copy, distribute and/or modify this document

|

||||

under the terms of the GNU Free Documentation License, Version 1.3

|

||||

or any later version published by the Free Software Foundation;

|

||||

with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts.

|

||||

A copy of the license is included in the section entitled "GNU

|

||||

Free Documentation License".

|

||||

|

||||

If you have Invariant Sections, Front-Cover Texts and Back-Cover Texts,

|

||||

replace the "with...Texts." line with this:

|

||||

|

||||

with the Invariant Sections being LIST THEIR TITLES, with the

|

||||

Front-Cover Texts being LIST, and with the Back-Cover Texts being LIST.

|

||||

|

||||

If you have Invariant Sections without Cover Texts, or some other

|

||||

combination of the three, merge those two alternatives to suit the

|

||||

situation.

|

||||

|

||||

If your document contains nontrivial examples of program code, we

|

||||

recommend releasing these examples in parallel under your choice of

|

||||

free software license, such as the GNU General Public License,

|

||||

to permit their use in free software.

|

||||

|

|

@ -0,0 +1,136 @@

|

|||

---

|

||||

title: How is Censored Libreboot implemented (ie. censored)?

|

||||

x-toc-enable: true

|

||||

...

|

||||

|

||||

Introduction

|

||||

============

|

||||

|

||||

For more context, please read the [Censored Libreboot c20230710 release

|

||||

announcement](https://libreboot.org/news/censored-libreboot20230710.html)

|

||||

|

||||

*Censored Libreboot* is a glimpse of the state Libreboot would

|

||||

be in, if it had never adopted the

|

||||

[Binary Blob Reduction Policy](https://libreboot.org/news/policy.html). In

|

||||

order to do this, many pages, and sources of information, were removed or

|

||||

heavily re-worded (censored) in this version, compared to regular Libreboot. The

|

||||

censored information/code would have never been permitted, under Libreboot's

|

||||

previous [Binary Blob Extermination Policy](https://web.archive.org/web/20221107235850/https://libreboot.org/news/policy.html)

|

||||

|

||||

Support for many mainboards has been removed, in this censored version. The

|

||||

website that you're reading

|

||||

is based on the regular Libreboot website at the time of the

|

||||

[Libreboot 20230625 release](https://libreboot.org/news/libreboot20230625.html).

|

||||

|

||||

Changes made in *Censored Libreboot*

|

||||

====================================

|

||||

|

||||

Almost all of the website changes can be seen here, in this diff:

|

||||

<https://codeberg.org/libreboot/lbwww/commit/23bf3b4c3d9473fd3fa6ee80907076667ea28ae7?style=split&whitespace=show-all>

|

||||

|

||||

The changes are so vast (about 8000 lines of text removed), that not all of them

|

||||

show by default in the above link, but you can click "Show More" at the bottom

|

||||

of that page. Codeberg is Libreboot's hosting provider for Git repositories, and

|

||||

the website is hosted in Git.

|

||||

|

||||

For a list of code changes, you can refer to the [Censored Libreboot c20230710

|

||||

release announcement](https://libreboot.org/news/censored-libreboot20230710.html)

|

||||

|

||||

The above link, and this page, demonstrate the *damage* that could be done to

|

||||

Libreboot, in the name of cult-like ideological purity. Libreboot's policy is

|

||||

simply to help as many people as possible install coreboot, with as few (or no)

|

||||

binary blobs as possible.

|

||||

|

||||

Deleted web pages, in *Censored Libreboot*:

|

||||

-------------------------------------------

|

||||

|

||||

All of these pages, which exist in the regular Libreboot website,

|

||||

do not exist in the *censored* Libreboot website:

|

||||

|

||||

* <https://libreboot.org/docs/hardware/hp2560p.html>

|

||||

* <https://libreboot.org/docs/hardware/hp2570p.html>

|

||||

* <https://libreboot.org/docs/hardware/hp8200sff.html>

|

||||

* <https://libreboot.org/docs/hardware/hp8300usdt.html>

|

||||

* <https://libreboot.org/docs/hardware/hp9470m.html>

|

||||

* <https://libreboot.org/docs/install/ivy_has_common.html>

|

||||

* <https://libreboot.org/docs/install/ivy_has_common.uk.html>

|

||||

* <https://libreboot.org/docs/install/ivy_internal.html>

|

||||

* <https://libreboot.org/docs/install/nvmutilimport.html>

|

||||

* <https://libreboot.org/docs/install/t420_external.html>

|

||||

* <https://libreboot.org/docs/install/t440p_external.html>

|

||||

* <https://libreboot.org/docs/install/x220_external.html>

|

||||

* <https://libreboot.org/docs/install/x230_external.html>

|

||||

* <https://libreboot.org/docs/linux/zfsbootmenu.html>

|

||||

* <https://libreboot.org/docs/maintain/porting.html>

|

||||

* <https://libreboot.org/docs/maintain/porting.uk.html>

|

||||

* <https://libreboot.org/freedom-status.html>

|

||||

* <https://libreboot.org/freedom-status.uk.html>

|

||||

* <https://libreboot.org/news/e6400nvidia.html>

|

||||

* <https://libreboot.org/news/freedom.html>

|

||||

* <https://libreboot.org/news/gm45microcode.html>

|

||||

* <https://libreboot.org/news/hp8200sff.html>

|

||||

* <https://libreboot.org/news/hp8200sff.uk.html>

|

||||

* <https://libreboot.org/news/hp_elitebooks.html>

|

||||

* <https://libreboot.org/news/libreboot20221214.html>

|

||||

* <https://libreboot.org/news/libreboot20230319.html>

|

||||

* <https://libreboot.org/news/libreboot20230413.html>

|

||||

* <https://libreboot.org/news/libreboot20230423.html>

|

||||

* <https://libreboot.org/news/libreboot20230625.html>

|

||||

* <https://libreboot.org/news/microcode.html>

|

||||

* <https://libreboot.org/news/policy.de.html>

|

||||

* <https://libreboot.org/news/policy.html>

|

||||

* <https://libreboot.org/news/policy.uk.html>

|

||||

* <https://libreboot.org/news/safety.html>

|

||||

|

||||

Heavily modified pages (not deleted)

|

||||

------------------------------------

|

||||

|

||||

These pages have been modified heavily (a few of these aren't pages, but are

|

||||

instead files like pandoc templates, used by Libreboot's static site

|

||||

generator, namely the [Untitled Static Site Generator](https://untitled.vimuser.org)):

|

||||

|

||||

* [/contrib.md](/contrib.html) (censored version), versus original: <https://libreboot.org/contrib.html>

|

||||

* [/contrib.uk.md](/contrib.uk.html) (censored version), versus original: <https://libreboot.org/contrib.uk.html>

|

||||

* [/docs/bsd/index.md](/docs/bsd/index.html) (censored version), versus original: <https://libreboot.org/docs/bsd/index.html>

|

||||

* [/docs/build/index.md](/docs/build/index.html) (censored version), versus original: <https://libreboot.org/docs/build/index.html>

|

||||

* [/docs/build/index.uk.md](/docs/build/index.uk.html) (censored version), versus original: <https://libreboot.org/docs/build/index.uk.html>

|

||||

* [/docs/hardware/e6400.md](/docs/hardware/e6400.html) (censored version), versus original: <https://libreboot.org/docs/hardware/e6400.html>

|

||||

* [/docs/hardware/ga-g41m-es2l.md](/docs/hardware/ga-g41m-es2l.html) (censored version), versus original: <https://libreboot.org/docs/hardware/ga-g41m-es2l.html>

|

||||

* [/docs/hardware/index.md](/docs/hardware/index.html) (censored version), versus original: <https://libreboot.org/docs/hardware/index.html>

|

||||

* [/docs/hardware/kgpe-d16.md](/docs/hardware/kgpe-d16.html) (censored version), versus original: <https://libreboot.org/docs/hardware/kgpe-d16.html>

|

||||

* [/docs/hardware/mac\_address.md](/docs/hardware/mac_address.html) (censored version), versus original: <https://libreboot.org/docs/hardware/mac_address.html>

|

||||

* [/docs/install/chromebooks.md](/docs/install/chromebooks.html) (censored version), versus original: <https://libreboot.org/docs/install/chromebooks.html>

|

||||

* [/docs/install/e6400.md](/docs/install/e6400.html) (censored version), versus original: <https://libreboot.org/docs/install/e6400.html>

|

||||

* [/docs/install/index.md](/docs/install/index.html) (censored version), versus original: <https://libreboot.org/docs/install/index.html>

|

||||

* [/docs/install/kgpe-d16.md](/docs/install/kgpe-d16.html) (censored version), versus original: <https://libreboot.org/docs/install/kgpe-d16.html>

|

||||

* [/docs/install/nvmutil.md](/docs/install/nvmutil.html) (censored version), versus original: <https://libreboot.org/docs/install/nvmutil.html>

|

||||

* [/docs/install/spi.md](/docs/install/spi.html) (censored version), versus original: <https://libreboot.org/docs/install/spi.html>

|

||||

* [/docs/install/spi\_generic.md](/docs/install/spi_generic.html) (censored version), versus original: <https://libreboot.org/docs/install/spi_generic.html>

|

||||

* [/docs/linux/index.md](/docs/linux/index.html) (censored version), versus original: <https://libreboot.org/docs/linux/index.html>

|

||||

* [/docs/maintain/index.md](/docs/maintain/index.html) (censored version), versus original: <https://libreboot.org/docs/maintain/index.html>

|

||||

* [/docs/maintain/testing.md](/docs/maintain/testing.html) (censored version), versus original: <https://libreboot.org/docs/maintain/testing.html>

|

||||

* [/docs/uboot/index.md](/docs/uboot/index.html) (censored version), versus original: <https://libreboot.org/docs/uboot/index.html>

|

||||

* [/docs/uboot/uboot-archlinux.md](/docs/uboot/uboot-archlinux.html) (censored version), versus original: <https://libreboot.org/docs/uboot/uboot-archlinux.html>

|

||||

* [/download.md](/download.html) (censored version), versus original: <https://libreboot.org/download.html>

|

||||

* [/download.uk.md](/download.uk.html) (censored version), versus original: <https://libreboot.org/download.uk.html>

|

||||

* [/faq.md](/faq.html) (censored version), versus original: <https://libreboot.org/faq.html>

|

||||

* [/faq.uk.md](/faq.uk.html) (censored version), versus original: <https://libreboot.org/faq.uk.html>

|

||||

* [/footer.de.include](/footer.de.include) (censored version), versus original: <https://libreboot.org/footer.de.include>

|

||||

* [/footer.include](/footer.include) (censored version), versus original: <https://libreboot.org/footer.include>

|

||||

* [/footer.uk.include](/footer.uk.include) (censored version), versus original: <https://libreboot.org/footer.uk.include>

|

||||

* [/footer.zh-cn.include](/footer.zh-cn.include) (censored version), versus original: <https://libreboot.org/footer.zh-cn.include>

|

||||

* [/index.de.md](/index.de.html) (censored version), versus original: <https://libreboot.org/index.de.html>

|

||||

* [/index.fr.md](/index.fr.html) (censored version), versus original: <https://libreboot.org/index.fr.html>

|

||||

* [/index.md](/index.html) (censored version), versus original: <https://libreboot.org/index.html>

|

||||

* [/index.uk.md](/index.uk.html) (censored version), versus original: <https://libreboot.org/index.uk.html>

|

||||

* [/index.zh-cn.md](/index.zh-cn.html) (censored version), versus original: <https://libreboot.org/index.zh-cn.html>

|

||||

* [/news/MANIFEST](/news/MANIFEST) (censored version), versus original: <https://libreboot.org/news/MANIFEST>

|

||||

* [/news/audit.md](/news/audit.html) (censored version), versus original: <https://libreboot.org/news/audit.html>

|

||||

* [/news/e6400.md](/news/e6400.html) (censored version), versus original: <https://libreboot.org/news/e6400.html>

|

||||

* [/news/e6400.uk.md](/news/e6400.uk.html) (censored version), versus original: <https://libreboot.org/news/e6400.uk.html>

|

||||

* [/news/usa-libre-part2.md](/news/usa-libre-part2.html) (censored version), versus original: <https://libreboot.org/news/usa-libre-part2.html>

|

||||

* [/template.de.include](/template.de.include) (censored version), versus original: <https://libreboot.org/template.de.include>

|

||||

* [/template.include](/template.include) (censored version), versus original: <https://libreboot.org/template.include>

|

||||

* [/template.uk.include](/template.uk.include) (censored version), versus original: <https://libreboot.org/template.uk.include>

|

||||

* [/template.zh-cn.include](/template.zh-cn.include) (censored version), versus original: <https://libreboot.org/template.zh-cn.include>

|

||||

|

||||

|

|

@ -0,0 +1,72 @@

|

|||

---

|

||||

title: Kontakt

|

||||

x-toc-enable: true

|

||||

...

|

||||

|

||||

**TODO: mailing lists, mastodon server and peertube account.**

|

||||

|

||||

User support

|

||||

============

|

||||

|

||||

IRC oder Reddit werden bevorzugt, sofern Du eine Support Anfrage hast (IRC empfohlen).

|

||||

Für Informationen bzgl. IRC and Reddit siehe unten.

|

||||

|

||||

Entwicklungs Diskussion

|

||||

======================

|

||||

|

||||

Eine Mailing Liste ist für die Zukunft in Planung. Bis dahin, siehe unter

|

||||

[der Git Seite](git.md) für Informationen wie Du dich an der Entwicklung beteiligen kannst.

|

||||

|

||||

Hier finden sich ebenso Anleitungen zum Senden von Patches (via Pull-Requests).

|

||||

|

||||

IRC Chatraum

|

||||

============

|

||||

|

||||

IRC ist hauptsächlich der Weg um Kontakt Libreboot Projekt aufzunehmen. `#libreboot` auf Libera

|

||||

IRC.

|

||||

|

||||

Webchat:

|

||||

<https://web.libera.chat/#libreboot>

|

||||

|

||||

Libera ist eines der grössten IRC Netzwerke, welches für Libre Software Projekte verwendet wird.

|

||||

Mehr Infos gibt es hier: <https://libera.chat/>

|

||||

|

||||

Wenn Du dich mit deinem bevorzugten IRC Klienten verbinden möchtest (z.B. weechat or irssi),

|

||||

anbei die Verbindungsdetails:

|

||||

|

||||

* Server: `irc.libera.chat`

|

||||

* Channel: `#libreboot`

|

||||

* Port (TLS): `6697`

|

||||

* Port (non-TLS): `6667`

|

||||

|

||||

Wir empfehlen, dass Du Port `6697` mit aktivierter TLS Verschlüsselung verwendest.

|

||||

|

||||

Es wird empfohlen SASL für die Authentifizierung zu verwenden. Diese Seiten auf der Libera

|

||||

Website erläutern wie dies funktioniert:

|

||||

|

||||

* WeeChat SASL Anleitung: <https://libera.chat/guides/weechat>

|

||||

* Irssi SASL Anleitung: <https://libera.chat/guides/irssi>

|

||||

* HexChat SASL Anleitung: <https://libera.chat/guides/hexchat>

|

||||

|

||||

Grundsätzlich solltest Du die Dokumentation der von Dir verwendeten IRC Software konsultieren.

|

||||

|

||||

Soziale Medien

|

||||

============

|

||||

|

||||

Libreboot existiert offiziell an vielen Orten.

|

||||

|

||||

Mastodon

|

||||

--------

|

||||

|

||||

Gründerin und Haupt-Entwicklerin, Leah Rowe, ist auf Mastodon:

|

||||

|

||||

* <https://mas.to/@libreleah>

|

||||

|

||||

Leah kann zudem unter dieser eMail kontaktiert werden:

|

||||

[leah@libreboot.org](mailto:leah@libreboot.org)

|

||||

|

||||

Reddit

|

||||

------

|

||||

|

||||

Hauptsächlich verwendet als Support Kanal und für Veröffentlichung von Neuigkeiten:

|

||||

<https://www.reddit.com/r/libreboot/>

|

||||

|

|

@ -0,0 +1,72 @@

|

|||

---

|

||||

title: Contact

|

||||

x-toc-enable: true

|

||||

...

|

||||

|

||||

**TODO: mailing lists, mastodon server and peertube account.**

|

||||

|

||||

User support

|

||||

============

|

||||

|

||||

IRC or Reddit are recommended, if you wish to ask for support (IRC recommended).

|

||||

See below for information about IRC and Reddit.

|

||||

|

||||

Development discussion

|

||||

======================

|

||||

|

||||

Mailing lists are planned for the future. For now, see notes

|

||||

on [the Git page](git.md) for information about how to assist with development.

|

||||

|

||||

Instructions are also on that page for sending patches (via pull requests).

|

||||

|

||||

IRC chatroom

|

||||

============

|

||||

|

||||

IRC is the main way to contact the libreboot project. `#libreboot` on Libera

|

||||

IRC.

|

||||

|

||||

Webchat:

|

||||

<https://web.libera.chat/#libreboot>

|

||||

|

||||

Libera is one of the largest IRC networks, used for Libre Software projects.

|

||||

Find more about them here: <https://libera.chat/>

|

||||

|

||||

If you wish to connect using your preferred client (such as weechat or irssi),

|

||||

the connection info is as follows:

|

||||

|

||||

* Server: `irc.libera.chat`

|

||||

* Channel: `#libreboot`

|

||||

* Port (TLS): `6697`

|

||||

* Port (non-TLS): `6667`

|

||||

|

||||

We recommend that you use port `6697` with TLS encryption enabled.

|

||||

|

||||

It is recommend that you use SASL for authentication. These pages on the Libera

|

||||

website tells you how:

|

||||

|

||||

* WeeChat SASL guide: <https://libera.chat/guides/weechat>

|

||||

* Irssi SASL guide: <https://libera.chat/guides/irssi>

|

||||

* HexChat SASL guide: <https://libera.chat/guides/hexchat>

|

||||

|

||||

In general, you should check the documentation provided by your IRC software.

|

||||

|

||||

Social media

|

||||

============

|

||||

|

||||

libreboot exists officially on many places.

|

||||

|

||||

Mastodon

|

||||

--------

|

||||

|

||||

The founder and lead developer, Leah Rowe, is on Mastodon:

|

||||

|

||||

* <https://mas.to/@libreleah>

|

||||

|

||||

Leah can also be contacted by this email address:

|

||||

[leah@libreboot.org](mailto:leah@libreboot.org)

|

||||

|

||||

Reddit

|

||||

------

|

||||

|

||||

Mostly used as a support channel, and also for news announcements:

|

||||

<https://www.reddit.com/r/libreboot/>

|

||||

|

|

@ -0,0 +1,72 @@

|

|||

---

|

||||

title: Зв'язок

|

||||

x-toc-enable: true

|

||||

...

|

||||

|

||||

**TODO: списки розсилки, сервер mastodon та обліковий запис peertube.**

|

||||

|

||||

Підтримка користувачів

|

||||

============

|

||||

|

||||

IRC або Reddit рекомендовані, якщо ви бажаєте попросити про допомогу (найкраще IRC).

|

||||

Дивіться інформацію нижче щодо IRC та Reddit.

|

||||

|

||||

Обговорення розробки

|

||||

======================

|

||||

|

||||

Списки розсилки плануються на майбутнє. Зараз, подивіться нотатки

|

||||

на [сторінці Git](git.md) для інформації щодо допомоги з розробкою.

|

||||

|

||||

На цій сторінці також знаходяться інструкції по відправці патчів (через pull request'и).

|

||||

|

||||

Кімната IRC

|

||||

============

|

||||

|

||||

IRC це головний спосіб зв'язку з проектом Libreboot. `#libreboot` на Libera

|

||||

IRC.

|

||||

|

||||

Веб-версія:

|

||||

<https://web.libera.chat/#libreboot>

|

||||

|

||||

Libera є однією з найбільших мереж IRC, використовуємих для проектів вільного програмного

|

||||

забезпечення. Знайти про них більше можна тут: <https://libera.chat/>

|

||||

|

||||

Якщо ви бажаєте під'єднатися за допомогою вашого улюбленного клієнта (такого як weechat або irssi),

|

||||

інформація для під'єднання наступна:

|

||||

|

||||

* Сервер: `irc.libera.chat`

|

||||

* Канал: `#libreboot`

|

||||

* Порт (TLS): `6697`

|

||||

* Порт (не TLS): `6667`

|

||||

|

||||

Ми радимо вам використовувати порт `6697` з увімкненим TLS шифруванням.

|

||||

|

||||

Рекомендовано використовувати SASL для аутентифікації. Ці сторінки на веб-сайті Libera

|

||||

пояснять вам як:

|

||||

|

||||

* Керівництво WeeChat SASL: <https://libera.chat/guides/weechat>

|

||||

* Керівництво Irssi SASL: <https://libera.chat/guides/irssi>

|

||||

* Керівництво HexChat SASL: <https://libera.chat/guides/hexchat>

|

||||

|

||||

Взагалі, вам варто перевірити документацію, яка передбачена вашою програмою IRC.

|

||||

|

||||

Соціальні мережі

|

||||

============

|

||||

|

||||

Libreboot офіційно існує в багатьох місцях.

|

||||

|

||||

Mastodon

|

||||

--------------------

|

||||

|

||||

Засновник та головний розробник, Лія Роу, є в Mastodon:

|

||||

|

||||

* <https://mas.to/@libreleah>

|

||||

|

||||

Також можливо зв'язатися з Лією за ії електронною адресою:

|

||||

[leah@libreboot.org](mailto:leah@libreboot.org)

|

||||

|

||||

Reddit

|

||||

------

|

||||

|

||||

Найбільше використовується як канал підтримки, та також для оголошення новин:

|

||||

<https://www.reddit.com/r/libreboot/>

|

||||

|

|

@ -0,0 +1,453 @@

|

|||

---

|

||||

title: Project contributors

|

||||

x-toc-enable: true

|

||||

...

|

||||

|

||||

This list does not necessarily reflect who is currently working on the project,

|

||||

but it lists some people who have contributed to the project in meaningful ways.

|

||||

|

||||

If we forgot to mention you here, let us know and we'll add you. (or if

|

||||

you don't want to be mentioned, let us know and we'll remove your

|

||||

entry)

|

||||

|

||||

Information about who works on libreboot, and how the project is run, can

|

||||

be found on this page: [who.md](who.md)

|

||||

|

||||

You can know the history of the libreboot project, simply by reading this page.

|

||||

It goes into detail about all of the major contributions to the project, and in

|

||||

general how the project was created (and who helped create it).

|

||||

|

||||

Leah Rowe

|

||||

---------

|

||||

|

||||

**Founder of the Libreboot project, and currently the lead developer.** Leah

|

||||

works on all aspects of libreboot, such as:

|

||||

|

||||

* General management. Leah handles all outside contributions to libreboot,

|

||||

reviews pull requests, deals with bug reports, delegates tasks when necessary

|

||||

or desirable. Leah controls the libreboot.org server infrastructure, hosted

|

||||

in her lab.

|

||||

* Leah has the final say on all decisions, taking input via discussion with

|

||||

members of the public, mostly on IRC. Leah oversees releases of libreboot,

|

||||

and generally keeps the project going. Without Leah, there would be no Libreboot!

|

||||

* The build system (lbmk, short for libreboot Make). This is the automated build

|

||||

system that sits at the heart of libreboot; it downloads, patches, configures

|

||||

and compiles the relevant components like coreboot, GRUB and generates

|

||||

the libreboot ROM images that you can find in release archives.

|

||||

* Upstream work on coreboot, when necessary (and other projects that libreboot

|

||||

uses). This means also working with people from outside of the libreboot

|

||||

project, to get patches merged (among other things) on the upstream projects

|

||||

that libreboot uses

|

||||

* Providing user support on IRC

|

||||

|

||||

Caleb La Grange

|

||||

---------------

|

||||

|

||||

**Secondary developer, number two to Leah.** Caleb is a full time libreboot developer

|

||||

with a narrower focus. Caleb focuses on several areas of development:

|

||||

|

||||

* Build system. Caleb is responsible for improving and fixing the libreboot Make build

|

||||

system. Specifically: binary blob management, automation, and reproducibility.

|

||||

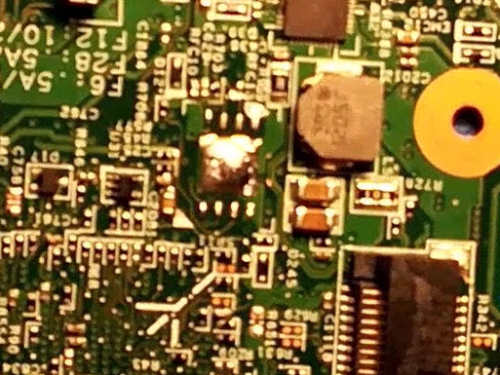

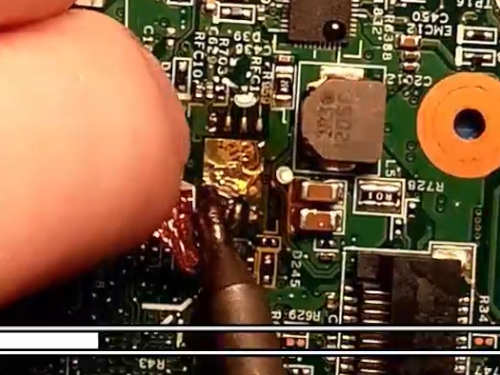

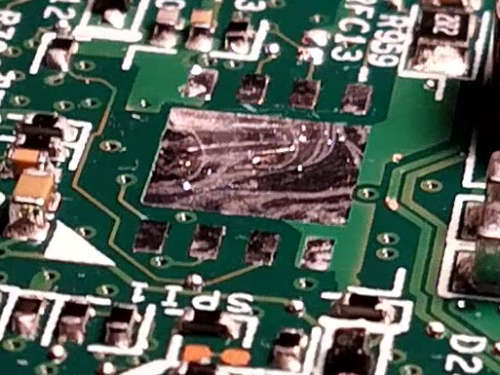

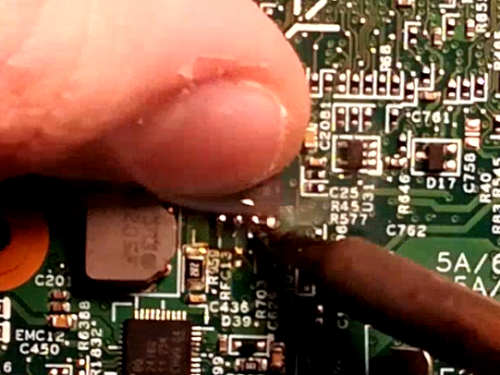

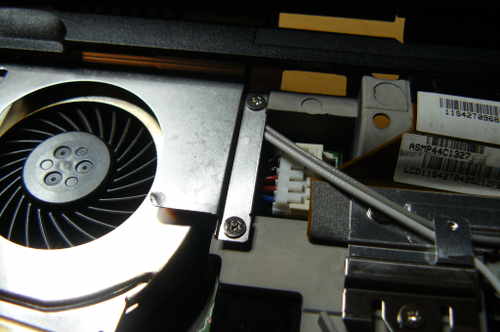

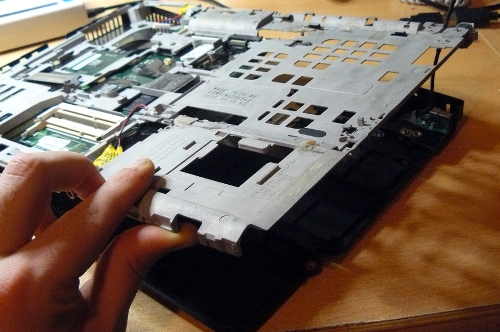

* Hardware modification. Caleb has a passion for hardware alteration; soldering,

|

||||

desoldering, and testing libreboot software on the resulting hardware.

|

||||

* Board porting. Anything supported in Coreboot can be ported to libreboot, Caleb

|

||||

will test and port any board he can get his hands on. Additionally, anyone can

|

||||

contact Caleb to generate libreboot roms for testing on their board.

|

||||

* Documentation. Caleb actively maintains documentation on the above areas of

|

||||

interest. Additionally, Caleb is responsible for disassembly guides with his own

|

||||

pictures and diagrams for several boards.

|

||||

* User support. Caleb is active on irc and willing to help any user interested in

|

||||

using libreboot or in need of help.

|

||||

* Project goals. Caleb collaborates with Leah on determining project goals.

|

||||

Leah has the final say in every decision.

|

||||

|

||||

External projects

|

||||

=================

|

||||

|

||||

Coreboot project

|

||||

----------------

|

||||

|

||||

Without coreboot, the libreboot project simply would not be possible.

|

||||

|

||||

The people and companies that work on coreboot are numerous, and they make the

|

||||

libreboot project what it is. The libreboot project makes heavy use of coreboot, to

|

||||

provide hardware initialization.

|

||||

|

||||

GRUB

|

||||

--------

|

||||

|

||||

GRUB is the bootloader used by libreboot. It goes without saying that the GRUB

|

||||

developers enable libreboot, through their work.

|

||||

|

||||

SeaBIOS

|

||||

-------

|

||||

|

||||

The libreboot firmware provides SeaBIOS as a payload option. SeaBIOS provides a

|

||||

legacy x86 BIOS implementation.

|

||||

|

||||

U-Boot

|

||||

------

|

||||

|

||||

Libreboot uses U-Boot as the coreboot payload on supported ARM Chromebooks.

|

||||

|

||||

Contributors in alphabetical order

|

||||

==================================

|

||||

|

||||

Alper Nebi Yasak

|

||||

----------------

|

||||

|

||||

Contributed the build system integration and documentation for using

|

||||

U-Boot as payload, and initial Libreboot ports of some ARM Chromebooks

|

||||

based on that.

|

||||

|

||||

Alper also does upstream development on U-Boot, e.g. continued an almost

|

||||

complete port of the `gru-kevin` board and got it merged upstream.

|

||||

|

||||

Alyssa Rosenzweig

|

||||

-----------------

|

||||

|

||||

Switched the website to use markdown in lieu of handwritten HTML and custom

|

||||

PHP. **Former libreboot project maintainer (sysadmin for libreboot.org).**

|

||||

|

||||

Alyssa wrote the original static site generator (shell scripts converting

|

||||

markdown to html, via pandoc) for libreboot.org. This static site generator has

|

||||

now been heavily modified and forked into a formal project, by Leah Rowe:

|

||||

|

||||

<https://untitled.vimuser.org/> (untitled is Leah's work, not Alyssa's, but it's based on

|

||||

Alyssa's original work on the static site generator that Libreboot used to use;

|

||||

the Libreboot website is now built with Untitled)

|

||||

|

||||

Andrew Robbins

|

||||

--------------

|

||||

|

||||

Worked on large parts of Libreboot's old build system and related documentation.

|

||||

Andrew joined the Libreboot project as a full time developer during June 2017,

|

||||

until his departure in March 2021.

|

||||

|

||||

I, Leah Rowe, am very grateful to Andrew Robbins for his numerous contributions

|

||||

over the years.

|

||||

|

||||

Arthur Heymans

|

||||

--------------

|

||||

|

||||

Merged a patch from coreboot into libreboot, enabling C3 and C4 power

|

||||

states to work correctly on GM45 laptops. This was a long-standing issue

|

||||

before Arthur's contribution. Arthur also fixed VRAM size on i945 on

|

||||

GM45 systems, allowing maximum VRAM allocation for the onboard GPUs on

|

||||

these systems, another longstanding issue in libreboot.

|

||||

|

||||

Arthur also did work on the Libreboot build system, when he was a member of the

|

||||

project. He still works on coreboot, to this day, and Libreboot greatly

|

||||

benefits from his work. His contributions to the coreboot project, and Libreboot,

|

||||

are invaluable.

|

||||

|

||||

Damien Zammit

|

||||

-------------

|

||||

|

||||

Maintains the Gigabyte GA-G41M-ES2L coreboot port, which is integrated

|

||||

in libreboot. Also works on other hardware for the benefit of the

|

||||

libreboot project.

|

||||

|

||||

Damien didn't work directly on Libreboot itself, but he worked heavily with

|

||||

Leah Rowe, integrating patches and new board ports into Libreboot, based on

|

||||

Damien's upstream work on coreboot.

|

||||

|

||||

Denis Carikli

|

||||

-------------

|

||||

|

||||

Based on the work done by Peter Stuge, Vladimir Serbinenko and others in

|

||||

the coreboot project, got native graphics initialization to work on the

|

||||

ThinkPad X60, allowing it to be supported in libreboot. Denis gave

|

||||

a lot of advice and helped found the libreboot project.

|

||||

|

||||

Denis was a mentor to Leah Rowe in the early days, when she founded the

|

||||

Libreboot project. A lot of the decisions taken, especially with the

|

||||

Libreboot build system (lbmk), were inspired from talks with Denis.

|

||||

|

||||

Denis taught Leah about registers used by Intel GPUs for backlight control. In

|

||||

the early days, the ThinkPad X60 and T60 laptops in Libreboot did not have

|

||||

backlight control working, so the brightness was always 100%. With Denis's help,

|

||||

Leah was able to get backlight controls working by reverse engineering the

|

||||

correct values to write in those registers. Based on this, a simple fix was

|

||||

written in coreboot; however, the fix just wrote directly to the register and

|

||||

didn't work with ACPI based brightness controls. Others in coreboot later

|

||||

improved it, making ACPI-based backlight controls work properly, based on this

|

||||

earlier work.

|

||||

|

||||

Ferass El Hafidi

|

||||

--------

|

||||

|

||||

Added cstate 3 support on macbook21, enabling higher battery life and cooler

|

||||

CPU temperatures on idle usage.

|

||||

|

||||

Also has a series of extensive improvements to the entire Libreboot system;

|

||||

for example, Ferass made the entire build system use POSIX `sh`, removing

|

||||

bashisms that previously plagued it.

|

||||

|

||||

This is IRC nick `f_` on Libreboot IRC. Cool guy!

|

||||

|

||||

Jeroen Quint

|

||||

------------

|

||||

|

||||

Contributed several fixes to the libreboot documentation, relating to

|

||||

installing on Arch-based systems with full disk encryption on libreboot

|

||||

systems.

|

||||

|

||||

Joshua Gay

|

||||

----------

|

||||

|

||||

Joshua is former FSF staff.

|

||||

|

||||

Joshua helped with the early founding of the Libreboot project, in his capacity

|

||||

(at that time) as the FSF's licensing and compliance manager. It was his job to

|

||||

review products sent into to the FSF for review; the FSF has a certification

|

||||

program called *Respects Your Freedom* (RYF) where the FSF will promote your

|

||||

company's products if it comes with all Free Software.

|

||||

|

||||

I, Leah Rowe, was initially just selling ThinkPad X60 laptops with regular

|

||||

coreboot on them, and this included CPU microcode updates. At the time, I didn't

|

||||

think much of that. Joshua contacted me, in his capacity at the FSF, and asked

|

||||

if I would be interested in the FSF's RYF program; I was very surprised that the

|

||||

FSF would take me seriously, and I said yes. This is what started the early

|

||||

work on Libreboot. Joshua showed me all the problems my products had, and from

|

||||

that, the solution was clear:

|

||||

|

||||

A project needed to exist, providing a fully free version of coreboot, without

|

||||

any binary blobs. At the time (and this is still true today), coreboot was not

|

||||

entirely libre software and shipped with binary blobs by default. In particular,

|

||||

CPU microcode updates were included by default, on all x86 machines. Working

|

||||

with Joshua who reviewed my work, I created a fully free version of coreboot.

|

||||

At first, it wasn't called Libreboot, and the work was purely intended for my

|

||||

company (at that time called Gluglug) to be promoted by the FSF.

|

||||

|

||||

Joshua used his media connections at the FSF to heavily promote my work, and

|

||||

on December 13th, 2013, the Libreboot project was born (but not called that).

|

||||

Joshua made sure that everyone knew what I was doing!

|

||||

|

||||

A few months later, the name *Libreboot* was coined, and the domain name

|

||||

*libreboot.org* was registered. At that point, the Libreboot project (in early

|

||||

2014) was officially born. Once again, Joshua provided every bit of help he

|

||||

could, heavily promoting the project and he even wrote this article on the FSF

|

||||

website, announcing it:

|

||||

|

||||

<https://web.archive.org/web/20171222063358/https://www.fsf.org/blogs/licensing/replace-your-proprietary-bios-with-libreboot>

|

||||

|

||||

Klemens Nanni

|

||||

-------------

|

||||

|

||||

Made many fixes and improvements to the GRUB configuration used in

|

||||

libreboot, and several tweaks to the build system.

|

||||

|

||||

Lisa Marie Maginnis

|

||||

-------------------

|

||||

|

||||

Lisa is a former sysadmin at the Free Software Foundation. In the early days of

|

||||

the project, she provided Leah with a lot of technical advice. She initially

|

||||

created Libreboot IRC channel, when Leah did not know how to

|

||||

use IRC, and also handed +F founder status to Leah for the channel. As an FSF

|

||||

sysadmin, it was Lisa's job to maintain a lot of the infrastructure used by

|

||||

Libreboot; at the time, mailing lists on the Savannah website were used by

|

||||

the Libreboot project. When Paul Kocialkowski was a member of the project in

|

||||

2016, she helped him get help from the FSF; he was the leader of the Replicant

|

||||

project at the time, which had funding from the FSF, and the FSF authorized him

|

||||

to use some of that funding for his work on Libreboot, thanks to Lisa's

|

||||

encouragement while she worked at the FSF.

|

||||

|

||||

Lisa also stepped in when Leah Rowe missed her LibrePlanet 2016 talk. Leah was

|

||||

scheduled to do a talk about Libreboot, but didn't show up in time. Lisa, along

|

||||

with Patrick McDermott (former Libreboot developer, who was present at that

|

||||

conference) did the talk in Leah's place. The talk was never recorded, but the

|

||||

Free Software Foundation has these photos of that talk on their LibrePlanet

|

||||

website (the woman with the blue hair is Lisa, and the long-haired dude with the

|

||||

moustache is Patrick):

|

||||

|

||||

<http://web.archive.org/web/20170319043913/https://media.libreplanet.org/u/libreplanet/m/session-02-c-mws-png-libreplanet-2016-sessions/>

|

||||

|

||||

<http://web.archive.org/web/20170319043915/https://media.libreplanet.org/u/libreplanet/m/session-02-c-wide-png-libreplanet-2016-sessions/>

|

||||

|

||||

Fun fact: Patrick is also the lead developer of ProteanOS, an FSF-endorsed

|

||||

embedded OS project: <http://proteanos.com/> (uses BusyBox and Linux-libre)

|

||||

|

||||

Leah Rowe ran *2* LibrePlanet workshops; one in 2015 and another in 2016, while

|

||||

visiting Boston, MA, USA on both occasions to attend these conferences. These

|

||||

workshops were for Libreboot installations. People came to both workshops, to

|

||||

have Libreboot installed onto their computers. As FSF sysadmin, at that time,

|

||||

Lisa provided all of the infrastructure and equipment used at those workshops.

|

||||

Without her help, those workshops would have not been possible.

|

||||

|

||||

When the ASUS KGPE-D16 mainboard (high-end server board) was ported to Libreboot,

|

||||

Leah, working with Timothy Pearson (the one who ported it), shared patches back

|

||||

and forth with Lisa around mid 2016, mostly raminit patches, to get the board

|

||||

running at the FSF offices. This work ultimately lead to a most wonderful

|

||||

achievement:

|

||||

|

||||

The FSF and GNU websites now run on