2023-07-10 15:43:08 +00:00

|

|

|

---

|

2024-08-31 21:28:18 +00:00

|

|

|

title: Gigabyte GA-G41M-ES2L desktop board

|

2023-07-10 15:43:08 +00:00

|

|

|

...

|

|

|

|

|

|

2024-08-31 21:28:18 +00:00

|

|

|

<div class="specs">

|

|

|

|

|

<center>

|

|

|

|

|

GA-G41M-ES2L

|

|

|

|

|

</center>

|

|

|

|

|

|

|

|

|

|

| ***Specifications*** | |

|

|

|

|

|

|----------------------------|------------------------------------------------|

|

|

|

|

|

| **Manufacturer** | Gigabyte |

|

|

|

|

|

| **Name** | GA-G41M-ES2L |

|

|

|

|

|

| **Released** | 2009 |

|

|

|

|

|

| **Chipset** | Intel G41 |

|

|

|

|

|

| **CPU** | Intel Core 2 Extreme/Quad/Duo,

|

|

|

|

|

Pentium Extreme/D/4 Extreme/4/Celeron |

|

|

|

|

|

| **Graphics** | Integrated |

|

|

|

|

|

| **Display** | None. |

|

|

|

|

|

| **Memory** | Up to 8GB (2x4GB DDR2-800) |

|

|

|

|

|

| **Architecture** | x86_64 |

|

|

|

|

|

| **Original boot firmware** | AWARD BIOS |

|

|

|

|

|

| **Intel ME/AMD PSP** | Present. Can be disabled |

|

|

|

|

|

| **Flash chip** | 2x8Mbit |

|

|

|

|

|

|

|

|

|

|

```

|

|

|

|

|

W+: Works without blobs;

|

|

|

|

|

N: Doesn't work;

|

|

|

|

|

W*: Works with blobs;

|

|

|

|

|

U: Untested;

|

|

|

|

|

P+: Partially works;

|

|

|

|

|

P*: Partially works with blobs

|

|

|

|

|

```

|

|

|

|

|

|

|

|

|

|

| ***Features*** | |

|

|

|

|

|

|----------------|---------------------------------------|

|

|

|

|

|

| **Internal flashing with original boot firmware** | W+ |

|

|

|

|

|

| **Display** | - |

|

|

|

|

|

| **Audio** | W+ |

|

|

|

|

|

| **RAM Init** | P+ |

|

|

|

|

|

| **External output** | P+ |

|

|

|

|

|

| **Display brightness** | - |

|

|

|

|

|

|

|

|

|

|

| ***Payloads supported*** | |

|

|

|

|

|

|---------------------------|-------|

|

|

|

|

|

| **GRUB** | Slow! |

|

|

|

|

|

| **SeaBIOS** | Works |

|

|

|

|

|

| **SeaBIOS with GRUB** | Works |

|

|

|

|

|

</div>

|

|

|

|

|

|

|

|

|

|

Introduction

|

|

|

|

|

============

|

|

|

|

|

|

|

|

|

|

This is a desktop board using intel hardware (circa \~2009, ICH7

|

|

|

|

|

southbridge, similar performance-wise to the ThinkPad X200. It can make

|

|

|

|

|

for quite a nifty desktop. Powered by Canoeboot.

|

|

|

|

|

|

|

|

|

|

IDE on the board is untested, but it might be possible to use a SATA HDD

|

|

|

|

|

using an IDE SATA adapter. The SATA ports do work, but it's IDE emulation. The

|

|

|

|

|

emulation is slow in DMA mode sia SeaBIOS, so SeaBIOS is configured to use PIO

|

|

|

|

|

mode on this board. This SeaBIOS configuration does not affect the Linux kernel.

|

|

|

|

|

|

|

|

|

|

You need to set a custom MAC address in Linux for the NIC to work.

|

|

|

|

|

In /etc/network/interfaces on debian-based systems like Debian or

|

|

|

|

|

Devuan, this would be in the entry for your NIC:\

|

|

|

|

|

hwaddress ether macaddressgoeshere

|

|

|

|

|

|

|

|

|

|

Alternatively:

|

|

|

|

|

|

|

|

|

|

cbfstool canoeboot.rom extract -n rt8168-macaddress -f rt8168-macaddress

|

|

|

|

|

|

|

|

|

|

Modify the MAC address in the file `rt8168-macaddress` and then:

|

|

|

|

|

|

|

|

|

|

cbfstool canoeboot.rom remove -n rt8168-macaddress

|

|

|

|

|

cbfstool canoeboot.rom add -f rt8168-macaddress -n rt8168-macaddress -t raw

|

|

|

|

|

|

|

|

|

|

Now you have a different MAC address hardcoded. In the above example, the ROM

|

|

|

|

|

image is named `canoeboot.rom` for your board. You can find cbfstool

|

|

|

|

|

under `cbutils/` after running the following command

|

|

|

|

|

in the build system:

|

|

|

|

|

|

|

|

|

|

./mk -d coreboot TREENAME

|

|

|

|

|

|

|

|

|

|

You can learn more about using the build system, cbmk, here:\

|

|

|

|

|

[Canoeboot build instructions](../build/)

|

|

|

|

|

|

|

|

|

|

RAM

|

|

|

|

|

===

|

|

|

|

|

|

|

|

|

|

**This board is very picky with RAM. If it doesn't boot, try an EHCI debug

|

|

|

|

|

dongle, serial usb adapter and null modem cable, or spkmodem, to get a

|

|

|

|

|

coreboot log to see if it passed raminit.**

|

|

|

|

|

|

|

|

|

|

Kingston 8 GiB Kit KVR800D2N6/8G with Elpida Chips E2108ABSE-8G-E

|

|

|

|

|

|

|

|

|

|

this is a 2x4GB setup and these work quite well, according to a user on IRC.

|

|

|

|

|

|

|

|

|

|

Nanya NT2GT64U8HD0BY-AD with 2 GiB of NT5TU128M8DE-AD chips works too.

|

|

|

|

|

|

|

|

|

|

Many other modules will probably work just fine, but raminit is very picky on

|

|

|

|

|

this board. Your mileage *will* fluctuate, wildly.

|

2023-07-10 15:43:08 +00:00

|

|

|

|

|

|

|

|

MAC ADDRESS

|

|

|

|

|

===========

|

|

|

|

|

|

|

|

|

|

NOTE: due to a bug in the hardware, the MAC address is hardcoded in

|

|

|

|

|

coreboot. Therefore, you must set your own MAC address in your

|

|

|

|

|

operating system.

|

|

|

|

|

|

|

|

|

|

Use [macchanger](http://www.gnu.org/software/macchanger) in your

|

|

|

|

|

distro, to set a valid MAC address. By doing this, your NIC should

|

|

|

|

|

work nicely.

|

|

|

|

|

|

|

|

|

|

Flash chip size {#flashchips}

|

|

|

|

|

===============

|

|

|

|

|

|

|

|

|

|

Use this to find out:

|

|

|

|

|

|

2024-01-27 22:35:38 +00:00

|

|

|

flashprog -p internal

|

2023-07-10 15:43:08 +00:00

|

|

|

|

|

|

|

|

Flashing instructions {#clip}

|

|

|

|

|

=====================

|

|

|

|

|

|

|

|

|

|

Refer to [spi.md](spi.md) for how to set up an SPI programmer for

|

|

|

|

|

external flashing. *You can only externally reprogram one of the chips

|

|

|

|

|

at a time, and you need to disable the chip that you're not flashing,

|

|

|

|

|

by connecting 3v3 to /CS of that chip, so you will actually need second test

|

|

|

|

|

clip or IC pin mini grabber.*

|

|

|

|

|

|

|

|

|

|

NOTE: on GA-G41M-ES2L, the flash shares a common voltage plane with the

|

|

|

|

|

southbridge, which draws a lot of current. This will cause under-voltage on

|

|

|

|

|

most SPI flashers, so do not use the 3.3V rail from your flasher. Do not

|

|

|

|

|

connect +3.3V to the chip. Instead, turn the board on and then turn it off by

|

|

|

|

|

holding the power button. With the board powered down, but plugged in, there

|

|

|

|

|

will be a 3.3V supply from the ATX PSU. You can then flash, but DO NOT connect

|

|

|

|

|

the +3.3V supply from your SPI flasher!

|

|

|

|

|

|

|

|

|

|

NOTE: You should use a resistor in series, between 1K to 10K ohms, for the 3.3v

|

|

|

|

|

connection to the CS pin. This is to protect from over-current.

|

|

|

|

|

|

|

|

|

|

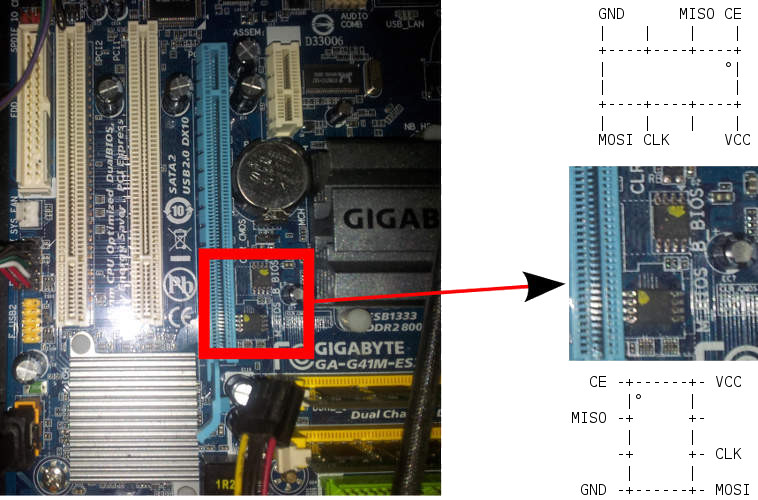

Here is an image of the flash chip:\

|

2023-10-26 00:10:41 +00:00

|

|

|

|

2023-07-10 15:43:08 +00:00

|

|

|

|

|

|

|

|

Internal flashing is possible. Boot with the proprietary BIOS and

|

2023-07-17 15:45:56 +00:00

|

|

|

GNU+Linux. There are 2 flash chips (one is backup).

|

2023-07-10 15:43:08 +00:00

|

|

|

|

|

|

|

|

Flash the first chip:

|

|

|

|

|

|

2024-01-27 22:35:38 +00:00

|

|

|

./flashprog -p internal:dualbiosindex=0 -w canoeboot.rom

|

2023-07-10 15:43:08 +00:00

|

|

|

|

|

|

|

|

Flash the second chip:

|

|

|

|

|

|

2024-01-27 22:35:38 +00:00

|

|

|

./flashprog -p internal:dualbiosindex=1 -w canoeboot.rom

|

2023-07-10 15:43:08 +00:00

|

|

|

|

|

|

|

|

NOTE: you can still boot the system with just the main flash chip

|

|

|

|

|

connected, after desoldering the backup chip. This has been tested while

|

2023-10-26 00:10:41 +00:00

|

|

|

Canoeboot was already installed onto the main chip.

|

2023-07-10 15:43:08 +00:00

|

|

|

|

|

|

|

|

NOTE: If you don't flash both chips, the recovery program from the default

|

|

|

|

|

factory BIOS will kick in and your board will be soft bricked. Make sure that

|

|

|

|

|

you flash both chips!

|

|

|

|

|

|

extreme cleanup / grandiose gesture

make canoeboot a truly GNU FSDG compliant coreboot distro,

by removing all overly positive reference to Libreboot;

what remains is technical in nature, so as to provide

historical context since Canoeboot is a fork of Libreboot.

I've stated before that I wish to take a more neutral tone

toward the FSF, in contrast to the *coldboot war* of 2023

when GNU Boot started.

Canoeboot was heavily linking to Libreboot, even going so far

as to call itself "inferior" and tell the reader to use

Libreboot.

From now on, Canoeboot will be maintained as though I actually

believed in FSF propoganda. I don't, but its users do. Treat

them with respect. My reason for providing Canoeboot is

precisely that I wish for such people to have a high quality

coreboot distro, much unlike the inferior *GNU Boot* project;

inferior because to this day, it's still based on very old

Libreboot, with not much changed (of any real substance)

relative to the Libreboot 20220710 release on which it forked.

In general, I've also found a lot of stragglers from when

Canoeboot started, where paragraphs referred to Libreboot that

should have actually referred to Canoeboot, or paragraphs

with Libreboot-specific information that does not make sense

in the Canoeboot project e.g. references to vendor scripts.

The resulting canoeboot.org will now look no different to any

typical reader than a typical FSF-aligned project.

There is a next stage to this, which will become apparent to

everyone if I have my way.

Signed-off-by: Leah Rowe <info@minifree.org>

2024-05-10 02:12:44 +00:00

|

|

|

NOTE: Canoeboot standardises on [flashprog](https://flashprog.org/wiki/Flashprog)

|

2024-01-27 22:35:38 +00:00

|

|

|

now, as of 3 May 2024, which is a fork of flashrom.

|